Rev.0 / Sep.2010

**DIAG00-00**

Copyright © 2010, Hitachi, Ltd.

# **DIAGNOSIS SECTION**

Copyright © 2010, 2012, Hitachi, Ltd.

**DIAG00-10**

# Contents

| DIAG01-10                                                                                            | Types of Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIAG02-10<br>DIAG02-10<br>DIAG02-20<br>DIAG02-30<br>DIAG02-60<br>DIAG02-70<br>DIAG02-80<br>DIAG02-90 | 2. DIAG Details 2.1 CUDG3 (Control Unit Diagnosis 3)/ FCDG3 (Fiber Channel module Diagnosis 3) 2.2 CUDG4 (Control Unit Diagnosis 4) 2.2.1 CUDG4 2.3 INLINE CUDG (INLINE Control Unit Diagnosis) 2.4 DKU INLINE 2.5 DKU PATH INLINE 2.6 LAN Checker                                                                                                                                                                                                                                                                  |

| DIAG03-10                                                                                            | 3. DIAG Parts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DIAG04-10<br>DIAG04-80<br>DIAG04-130<br>DIAG04-130<br>DIAG04-170<br>DIAG04-210<br>DIAG04-260         | 4.3 DKU PATH INLINE Test Procedures 4.3.1 A0 routine Test Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DIAG05-10<br>DIAG05-10<br>DIAG05-20<br>DIAG05-30<br>DIAG05-40<br>DIAG05-60<br>DIAG05-61              | <ul> <li>5. DIAG Trouble shooting</li> <li>5.1 CUDG Trouble shooting</li> <li>5.1.1 CUDG3 Trouble shooting</li> <li>5.1.2 CUDG4 Trouble shooting</li> <li>5.1.3 INLINE CUDG Trouble shooting</li> <li>5.1.4 CACHE PCB, CACHE MEMORY MODULE Trouble shooting</li> <li>5.1.5 Judgement of MODID Incorrectness and Recovery Procedure in Case of Two Successive Errors of Replacement/Installation of CACHE/MPB/SSVP</li> <li>5.2 DKU INLINE Trouble shooting</li> <li>5.3 DKU BATH INLINE Trouble shooting</li> </ul> |

| DIAG05-80  DIAG06-10  DIAG06-70  DIAG06-230  DIAG06-230  DIAG06-950                                  | <ul> <li>5.3 DKU PATH INLINE Trouble shooting</li> <li>6. DIAG Errors</li> <li>6.1 DKU INLINE Error Code List</li> <li>6.2 PATH INLINE Error Code List</li> <li>6.3 CUDG error code list</li> <li>6.3.1 CUDG3 error code list</li> <li>6.3.2 CUDG4 error code list</li> </ul>                                                                                                                                                                                                                                       |

Rev.0 / Sep.2010

**DIAG01-10**

# 1. Types of Diagnosis

This subsystem's diagnostics consist of the six types of test routines listed below. They are selected according to the purpose and the part to be tested.

Table 1-1 Diagnostics Test Routines

| Item<br>No. | Type                  | Diagnosis                                              | Part                                  | Timing                                                                                         |

|-------------|-----------------------|--------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------|

| 1           | CUDG3/<br>FCDG3       | Initial diagnoses                                      | CHA, DKA,<br>CACHE MEMORY,<br>MP, ESW | When DKC is powered on or CHA or DKA or MP is replaced or installed (automatic)                |

| 2           | CUDG4                 | Functional diagnoses executed when the unit is offline | CHA, DKA,<br>CACHE MEMORY,<br>MP, ESW | During installation (as specified by service personnel)                                        |

| 3           | INLINE<br>CUDG        | Functional diagnoses executed when the unit is online  | CACHE MEMORY                          | When Cache is replaced or installed (automatic)                                                |

| 4           | DKU<br>INLINE         | DKA-HDU functional (connection) check                  | DKA, SSW, HDD                         | When an HDD is replaced (automatic) or during installation (as specified by service personnel) |

| 5           | DKU<br>PATH<br>INLINE | <b>↑</b>                                               | DKA, SSW, HDDFAN                      | <b>↑</b>                                                                                       |

| 6           | LAN                   | LAN check between DKC and SVP                          | SVP, SSVP, DKA, CHA                   | When LAN communication error or communication time-out error is occurred.                      |

Copyright © 2010, Hitachi, Ltd.

Rev.0 / Sep.2010

**DIAG02-10**

Copyright © 2010, Hitachi, Ltd.

# 2. DIAG Details

# 2.1 CUDG3 (Control Unit Diagnosis 3)/ FCDG3 (Fiber Channel module Diagnosis 3)

CUDG3/FCDG3 is a collection of test routines that are started at system start time (when the unit power is turned on), prior to the execution of the main program and automatically checks the basic functions of the unit to ensure the normal hardware operation of the system. The CUDG3/FCDG3 routines are listed in Table 2.1-1.

Table 2.1-1 CUDG3/FCDG3 Test Routines

| Item<br>No. | Routine Name | Function                                                                                               |  |

|-------------|--------------|--------------------------------------------------------------------------------------------------------|--|

| 1           | CUDG3B       | Local memory/ Processor diagnosis                                                                      |  |

| 2           | CUDG3C1      | Processor diagnosis                                                                                    |  |

| 3           | ESW Test1    | ESW common part diagnosis by a delegated processor                                                     |  |

| 4           | ESW Test2    | ESW occupation part diagnosis by a delegated processor in MPPK                                         |  |

| 5           | CUDG3C6      | Shared resource diagnosis by a delegated processor (CACHE)                                             |  |

| 6           | CHA/DKA Test | CHA/DKA diagnosis by a delegated processor                                                             |  |

| 7           | FCDG3        | CS, for Serial/Parallel port, read/write test, internal diagnostic test, communication diagnostic test |  |

Rev.0 / Sep.2010

**DIAG02-20**

# 2.2 CUDG4 (Control Unit Diagnosis 4)

CUDG4 supports Cache memory read after full write tests and other tests that cannot be covered by CUDG3/FCDG3. It is executed by the service personnel when the unit is offline. After CUDG4, the subsystem PS OFF/ON is mandatory in order to return to ONLINE status of the subsystem.

Copyright © 2010, Hitachi, Ltd.

Copyright © 2010, Hitachi, Ltd.

#### 2.2.1 CUDG4

If CUDG4 is executed, it may become impossible to guarantee the data on Cache Memory.

- ① Execute PS OFF and ON before CUDG Test. The data on CACHE is stored to HDD.

- ② Be sure the check the validity of CUDG Test to Technical Support Division before CUDG Test.

The CUDG4 test routines are listed in Table 2.2.1-1.

The CUDG4 run option are listed in Table 2.2.1-2.

Table 2.2.1-1 CUDG4 Test Routines

| Item<br>No. | Test Item (*2)              | Function                                                                                                 | Module extending |

|-------------|-----------------------------|----------------------------------------------------------------------------------------------------------|------------------|

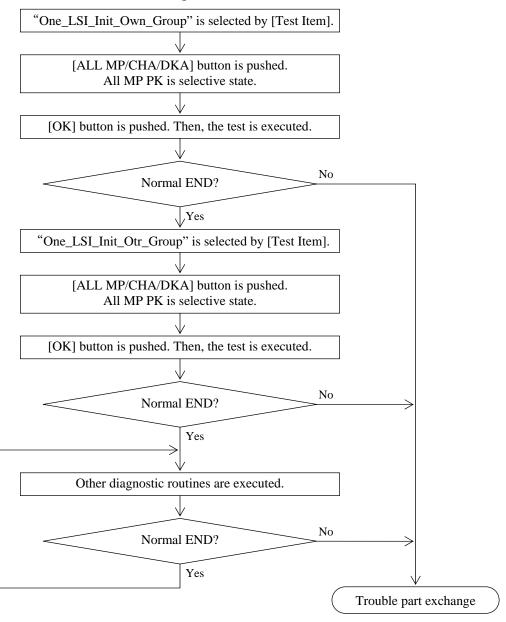

| 1           | One_LSI_Init_Own_Group (*1) | The hard initialization of the own- module is executed by specified MP.                                  | None             |

| 2           | One_LSI_Init_Otr_Group (*1) | The hard initialization of the other-module is executed by specified MP. (Use by two module composition) | Done             |

| 3           | One_MP_PK_Test              | Specified MP PK is diagnosed.                                                                            | None             |

| 4           | One_ESW_PK_Test             | ESW PK in own-module is diagnosed by specified MP.                                                       | None             |

| 5           | All_CM_PK_Test              | CM PK and CACHE MEMORY in own-module are diagnosed by specified MP.                                      | None             |

| 6           | All_CHADKA_PK_Test          | Specified CHA/DKA PK is diagnosed by specified MP.                                                       | Done             |

| 7           | All_Diag1_Test              | The data transfer diagnosis between each PK is executed by specified MP.                                 | Done             |

| 8           | All_Cache_mem_Test1         | CACHE MEMORY in own-module are diagnosed by specified MP. (Diagnosis by micro function)                  | None             |

| 9           | All_Cache_Mem_Test2         | CACHE MEMORY in own-module are diagnosed by specified MP. (Diagnosis by hard function)                   | None             |

(\*1) It is necessary to execute "One\_LSI\_Init\_Own\_Group" and "One\_LSI\_Init\_Otr\_Group" in advance of other diagnostic routines.

In the execution of "One\_LSI\_Init\_Own\_Group" and "One\_LSI\_Init\_Otr\_Group", select all MP.

Execute other diagnostic routines after confirming the normal termination of "One\_LSI\_Init\_Own\_Group" and "One\_LSI\_Init\_Otr\_Group".

(\*2) Test Item that starts by "One" is sequentially executed when two or more MP is selected, and Test Item that starts by "All" is executed in parallel.

#### **DIAG02-40**

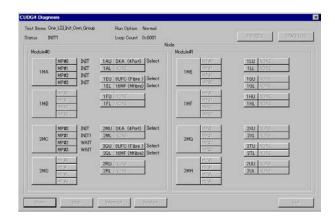

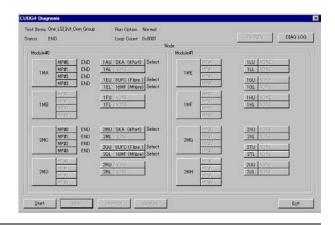

# [CUDG4 Set Parameter Screen]

Rev.0 / Sep.2010

**DIAG02-50**

Table 2.2.1-2 CUDG4 Run Option

| Item No. | Run Option                      | If an error is not detected                                                | If an error is detected                                                                                                                                                        |  |

|----------|---------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1        | Normal                          | CUDG test will be executed only once.                                      | CUDG test will be terminated when an error is detected. And the error detail will be displayed on the SVP screen. After finishing the CUDG function, please refer to Diag log. |  |

| 2        | Loop(Limit less)<br>(*1)(*2)    | CUDG test will be executed continuously.                                   | CUDG test will be terminated when an error is detected. And the error detail will                                                                                              |  |

| 3        | Looptimes (*2)                  | The CUDG test will be executed up to the specified frequency. $(2\sim999)$ | be displayed on the SVP screen. After finishing the CUDG function, please refer to Diag log.                                                                                   |  |

| 4        | Error Loop(Limit less) (*1)(*2) | CUDG test will be executed continuously.                                   | CUDG test continues. And an error detail is displayed on the SVP screen when                                                                                                   |  |

| 5        | Error Looptimes (*2)            | The CUDG test will be executed up to the specified frequency. $(2\sim999)$ | CUDG test ends. But the CUDG will continues testing.                                                                                                                           |  |

| 6        | Error Log(Limit less) (*1)(*2)  | CUDG test will be executed continuously.                                   | CUDG test continuous. And an error detail will be displayed on the SVP screen when                                                                                             |  |

| 7        | Error Logtimes (*2)             | The CUDG test will be executed up to the specified frequency. $(2\sim999)$ | CUDG test ends. After finishing the CUDG function, refer to Diag log.                                                                                                          |  |

- \*1: When "Limit less" is selected, Test Item that starts by "One" is executed only by head MP# in selected MP. Please specify the test frequency when you operate Test Item that starts by "One" with two or more MP.

- \*2: Please push [STOP] button when you stop the test continuously executed. [STOP] button might not be accepted unusually. At that time, please push [STOP] button again. It is likely to hang for a few minutes until stopping though the diagnosis time is different according to Test Item.

Copyright © 2010, Hitachi, Ltd.

Rev.0 / Sep.2010 **DIAG02-60**  Copyright © 2010, Hitachi, Ltd.

# 2.3 INLINE CUDG (INLINE Control Unit Diagnosis)

INLINE CUDG checks the validity of Cache memory when the entire disk subsystem is running normally. The INLINE CUDG test routines are listed in Table 2.3-1.

Table 2.3-1 INLINE CUDG Test Routines

| Item<br>No. | Routine Name        | Function            |

|-------------|---------------------|---------------------|

| 1           | Cache memory system | CACHE PCB diagnosis |

Rev.0 / Sep.2010

**DIAG02-70**

Copyright © 2010, Hitachi, Ltd.

#### 2.4 DKU INLINE

The DKU INLINE of test routines are used to ensure that the HDD is accessible to the Disk Controller when one is installed (a new or as an additional unit). This INLINE facility is also executed when a HDD is replaced during online processing as part of the recovery procedure to ensure that the HDD is normal. In this case, this INLINE facility runs automatically (with no SVP manipulation). The test routines are listed in Table 2.4-1.

Table 2.4-1 DKU INLINE Test Routines

| Routine<br>ID | Test Name | Function                                                                  |

|---------------|-----------|---------------------------------------------------------------------------|

|               |           |                                                                           |

| C1            | TEST UNIT | Issues the TEST UNIT READY to the HDD and verifies that the status is     |

|               | READY&    | GOOD or CHECK.                                                            |

|               | REQ.SENSE |                                                                           |

| C2            | INQUIRY   | Checks the HDU-specific information.                                      |

| C4            | HDU SELF  | Issues the SEND DIAG (Self Test) command to the HDD and verifies that the |

|               | TEST      | terminates normally.                                                      |

#### Notes:

- All logical devices must be in the "BLOCKED" state. If not, the test routine will error-terminate. Refer to from SVP02-890 of SVP SECTION for all logical devices blocked.

- The previous test routines must have been terminated normally before the pertinent test routine is started.

- The Disk Controller should have been powered on normally.

# **DIAG02-80**

#### 2.5 DKU PATH INLINE

The DKU Path Inline is used to check that the connection between the DKA and the HDU is correct. The DKU path inline test routines are shown in Table 2.5-1.

Moreover, the thing for which only the diagnostic routine shown in diagnostic order at the time of introduction is performed at the time of equipment introduction. It is not performing manually, since diagnosis is automatically performed in extension processing when extending DKU to an established subsystem. (It will become a serious error if it performs manually.)

| Introduction diagnostic | Routine<br>ID | Execution propriety | Test Name                 | Function                                                                                                     | M                  |                         | xecution ti              | me                       |

|-------------------------|---------------|---------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|--------------------------|--------------------------|

| order                   |               | under<br>ONLINE     |                           |                                                                                                              | 1HDD               | 16HDD                   | 32HDD                    | 256HDD                   |

| 1                       | A0            | 0 (*5)              | Path Address TEST1        | Checks whether the selected DKA and HDU are correctly connected.                                             | About 1 min.       | About 1 min.            | About 1 min.             | About 1 min.             |

| _                       | A2            | ×                   | Failed HDD detection test | Detects the failed HDD and recovers it by using the reset function when an A0 10 or A0 20 error occurs. (*2) | About 10 sec.      | About 2 min.            | About 3 min.             | About<br>13 min.         |

| 2 (*1)                  | A3            | ×                   | HDD READ TEST             | Executes the Read Test of the mounted HDD is executed. (*3)                                                  | About 10 sec. (*6) | About<br>3 min.<br>(*6) | About 5 min. (*6)        | About<br>13 min.<br>(*6) |

|                         |               |                     |                           |                                                                                                              | About 15 sec. (*7) | About<br>4 min.<br>(*7) | About<br>10 min.<br>(*7) | About 35 min. (*7)       |

Table 2.5-1 DKU PATH INLINE Test Routine

#### Notes:

- \*1: Do not perform when the subsystem is online, or when HDD installation or when DKU installation are performed. Only run this routine during a new Install, and before customer data is present.

- \*2: The routine A2 forcibly blocks the port of the HDD by using the individual SCSI RESET function for the HDD connected to the designated port of the selected DKA. Therefore, you must not do this operation expect for finding the factor of A010/A020 error.

- \*3: The routine A3 executes Read Test to all equipped HDD. Therefore, you must not execute this operation during ONLINE.

- \*4: The maximum execution times here is the time when communication is normal. Communication time-out, is 3 minutes plus the above time.

- \*5: Do not perform it manually, since diagnosis is automatically performed in the subsystem maintenance processing.

- \*6: The execution time in Standard model.

- \*7: The execution time in High performance model.

Rev.0 / Sep.2010

**DIAG02-90**

# 2.6 LAN Checker

LAN checker analyses the LAN connection between DKC and SVP to determine whether the LAN error is caused by the physical connection or the communication software.

Table 2.6-1 LAN Checker Test

| # | Test Name | Function                                                                                                                                          | Maximum execution time |

|---|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1 |           | Checker executes "Ping" to all MPs. If the result is "no-response", for an MP, the physical connection error has occurred between the MP and SVP. | 2 min.<br>(1 MP)       |

| 2 |           | Checker executes the communication between SVP and MPs whose result of #1 is "responded".                                                         |                        |

Copyright © 2010, Hitachi, Ltd.

Copyright © 2010, Hitachi, Ltd.

# 3. DIAG Parts

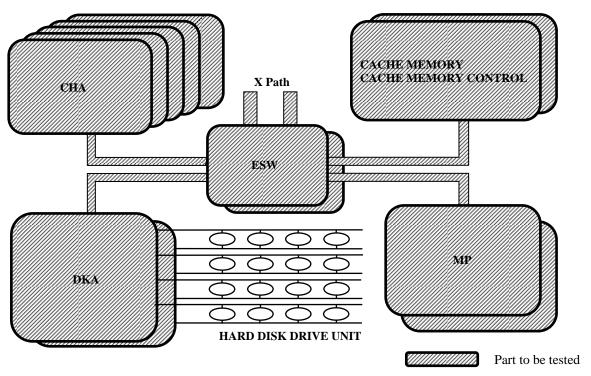

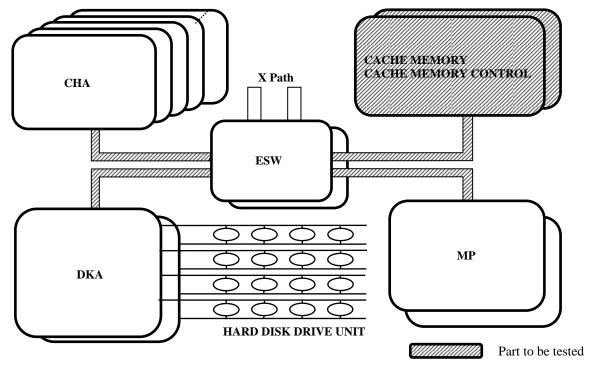

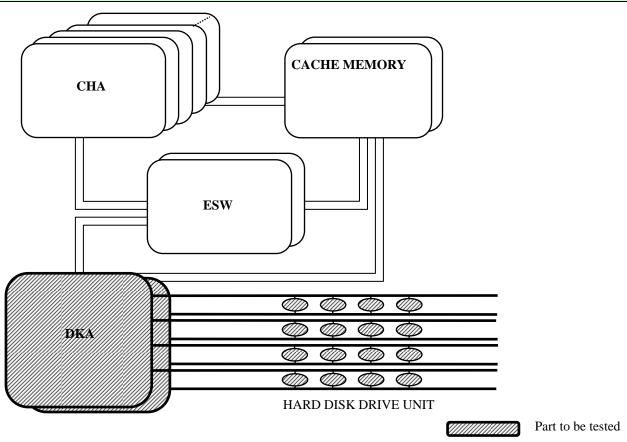

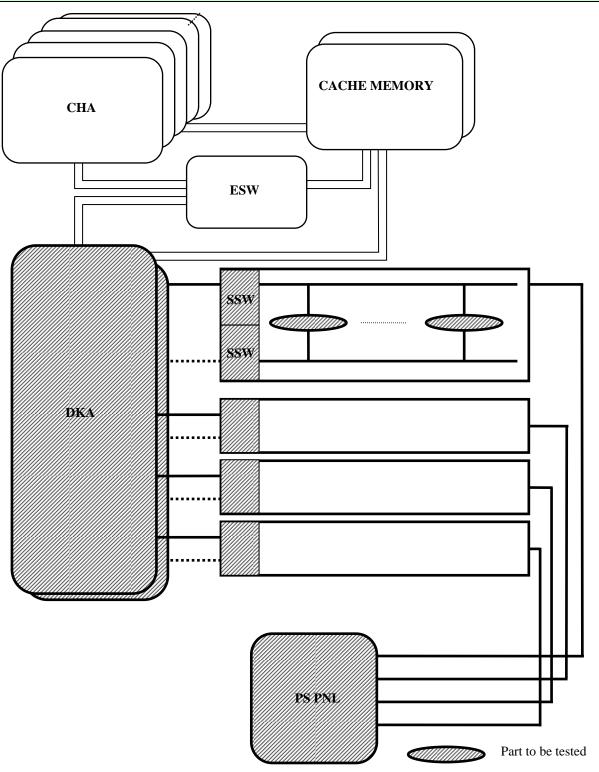

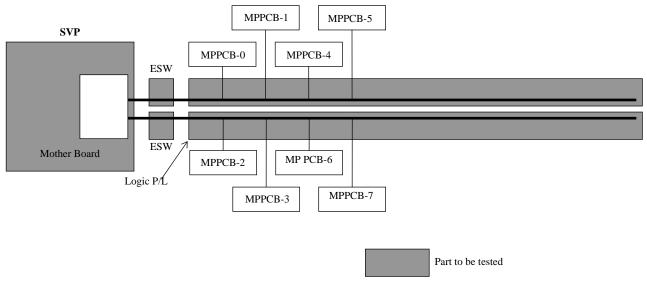

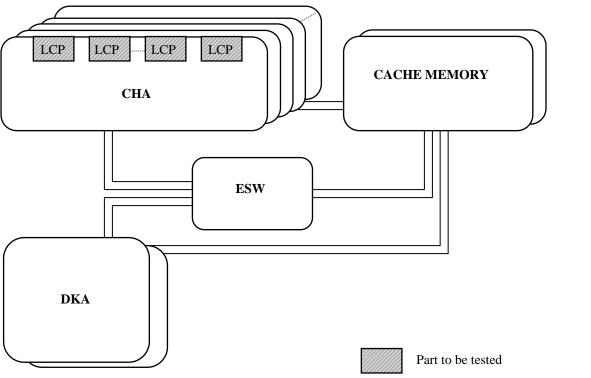

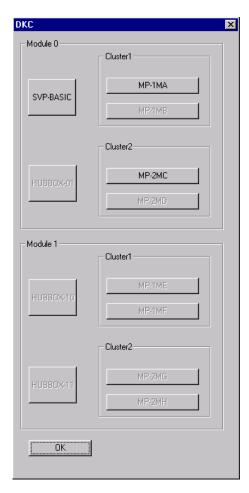

The parts that are diagnosed by the DIAG test routines are shown in Figs. 3-1 through 3-5.

Fig. 3-1 Parts Subject to CUDG3/CUDG4 Tests

Fig. 3-2 Parts Subject to INLINE CUDG Tests

Rev.0 / Sep.2010

**DIAG03-20**

Copyright © 2010, Hitachi, Ltd.

Fig. 3-3 Parts Subject to DKU INLINE Tests

# **DIAG03-30**

Fig. 3-4 Parts Subject to DKU PATH INLINE Tests

Fig. 3-5 Parts Subjects to LAN check

Fig. 3-6 Parts Subject to LCDG4 Tests

Rev.0 / Sep.2010

**DIAG04-10**

Copyright © 2010, Hitachi, Ltd.

# 4. DIAG Test Procedures (SVP Operations)

## 4.1 CUDG4 Test Procedures

# A CAUTION

- ① If CUDG4 is executed, it may become impossible to guarantee the data on Cache Memory.

- Execute PS OFF and ON before CUDG Test. The data on CACHE is stored to HDD.

- Be sure to check the validity of CUDG Test to Technical Support Division before CUDG Test.

- ② Powering off/on is required owing to the performance of this operation.

- 1. <Execute PS OFF> Turn off the DKC subsystem by performing the PS-OFF operation.

- <PS ON with CE-Mode> Set the Maintenance Jumpers to CE Mode connectors, then execute PS ON.

- 3. <SVP Initial screen> Refer to SVP01-120.

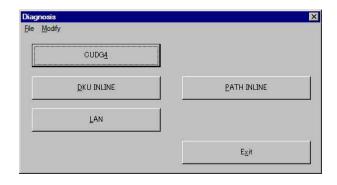

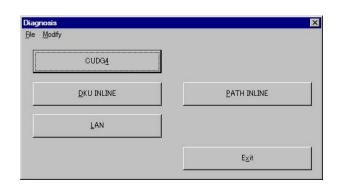

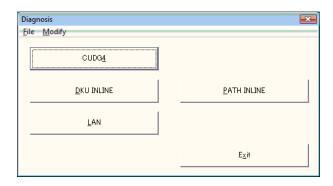

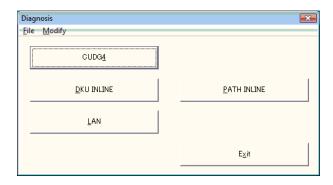

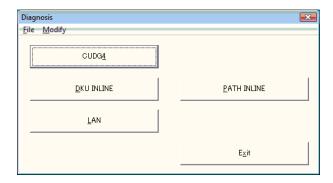

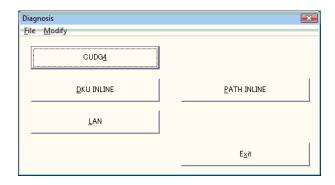

- 4. <Operation mode change> Change the mode to [Modify Mode]. Select (CL) [Diagnosis].

- 5. <Activating CUDG> Select (CL) [CUDG4].

Rev.0 / Sep.2010

**DIAG04-20**

Copyright © 2010, Hitachi, Ltd.

#### 6. <Password>

# **A** CAUTION

Ask the technical support division about the appropriateness of the operation, and input a password after getting an approval of executing the operation.

If you want to continue this process, enter the password, and select (CL) [OK].

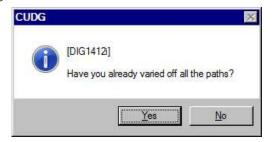

7. < Confirming that the channel path has been varied off> An inquiry "Have you already varied off all the paths?" is displayed. Vary off the channel path, then select (CL) the [Yes] button.

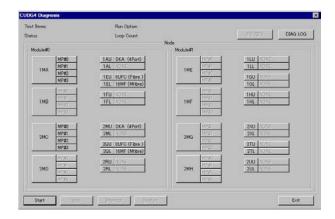

8. <Start of CUDG4 test> Select (CL) [Start].

Rev.0 / Sep.2010

**DIAG04-30**

Copyright © 2010, Hitachi, Ltd.

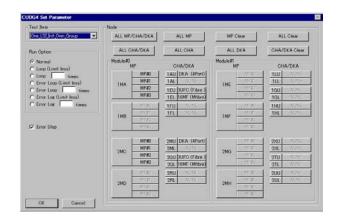

# 9. <Setting test parameters>

Select a Test Item, Run Option, test object CHA/DKA and a test object processor from Test Item.

Select (CL) the [OK] button after all the above selections are made.

[Test Item]

Refer to DIAG02-30.

[Run Option]

Refer to DIAG02-50.

[Error Stop]

When the error is detected when two or more MP (processor) is selected and Test Item that starts by "One" is executed, the execution of the following MP is stopped.

[Test object processors]

ALL MP/CHA/DKA : The test is executed on all the processors and all the CHA/DKA

in the configuration.

ALL MP : The test is executed on all the processors in the configuration.

ALL CHA/DKA : The test is executed on all the CHA/DKA in the configuration.

ALL CHA : The test is executed on all the CHA in the configuration.

ALL DKA : The test is executed on all the DKA in the configuration.

MP Clear : Release of processor selection.

ALL Clear : Release of all selection.

CHA/DKA Clear : Release of CHA/DKA selection.

The mounted processor and CHA/DKA is displayed on Equip. Selected processor or CHA/DKA is displayed in reverse video. When you want to select a specified processor or CHA/DKA in the configuration, Select a processor or CHA/DKA directly.

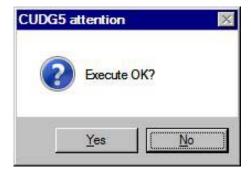

## 10. <Confirmation of execution>

The execution confirmation message is displayed. Select (CL) [Yes].

Rev.0 / Sep.2010

**DIAG04-40**

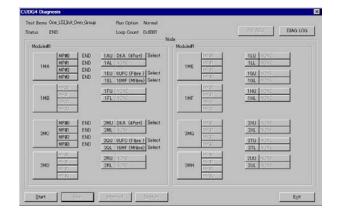

11. <Displaying CUDG4 loading>

Statuses of INIT1, INIT2, INIT3 and WAIT are displayed on the 'CUDG4' screen.

If Load is done once, it is not executed until returning to the Diagnosis screen of step 5.

Copyright © 2010, Hitachi, Ltd.

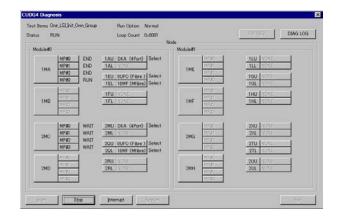

12. <Displaying Run>

State of the run is displayed on the 'CUDG4' screen.

Normal end state:

'WAIT'->'RUN'->'END'

Abnormal end state:

'WAIT'->'RUN'->'ERR'

Normal end----- Go to step 11. Abnormal end----- Go to step 10.

Rev.0 / Sep.2010

#### **DIAG04-50**

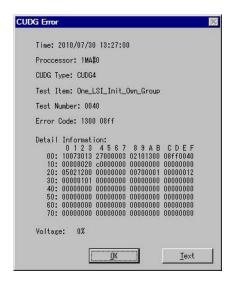

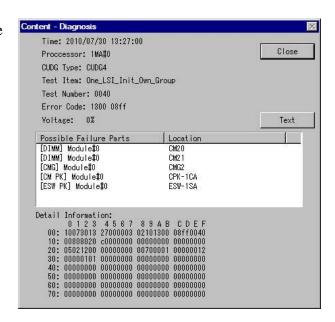

# 13. < Displaying error>

If an error occurs in CUDG4 test, the CUDG Error window is displayed.

To execute CUDG4 again, go to step 15 -> step 16 -> step 5. To terminate CUDG4, go to step 15 -> step 16 -> step 17.

Copyright © 2010, Hitachi, Ltd.

The error screen accumulated by selecting the [DIAG LOG] button on the CUDG4 Diagnosis screen is displayed.

#### **DIAG04-60**

# 14. <Displaying End>

Status "END" is displayed for the processor that CUDG4 test ends.

To continue CUDG4, go to step 8. To terminate CUDG4, go to step 15.

15. <Displaying Exit> Select (CL) [Exit].

# 16. <PS-OFF>

Turn off the DKC subsystem by performing the PS-OFF operation following the displayed instruction "Turn off the DKC subsystem.", then select (CL) the [OK] button. To continue CUDG4, PS-ON operation and go to step 5. To terminate CUDG4, go to step 17.

17. < Detaching of Maintenance Jumper>

The Maintenance Jumper is detached from the CE-Mode connector.

Rev.0 / Sep.2010

#### **DIAG04-70**

# 18. < Reboot the PC and PS-ON>

- 'Diagnosis' window is displayed.

- Close the window

- Reboot the PC

- Power Off SVP (See SVP01-160.)

- Power On SVP (See SVP01-150.)

- PS-ON

Copyright © 2010, Hitachi, Ltd.

End of CUDG4 operation.

Rev.0 / Sep.2010

Copyright © 2010, Hitachi, Ltd.

#### **DIAG04-80**

# **4.2 DKU INLINE Test Procedures**

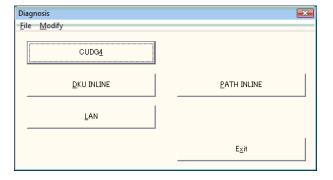

- 1. <Initial screen>

- <Operation mode change>

Change the mode to [Modify Mode].

Select (CL) [Diagnosis].

- 3. <Select 'DKU INLINE'>

The 'Diagnosis' window is displayed.

And select (CL) [DKU INLINE].

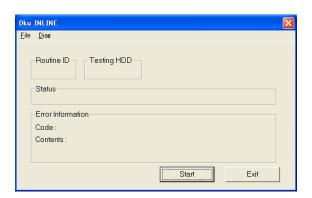

4. <Select [Start]>

Select (CL) [Start].

Rev.0 / Sep.2010

**DIAG04-90**

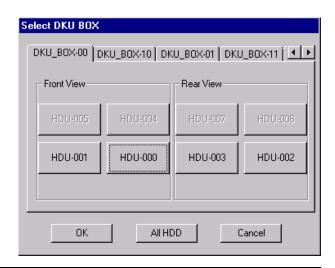

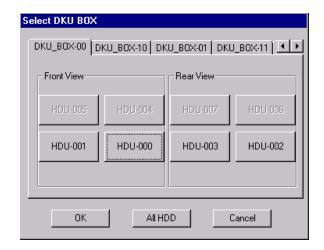

5. <Select UNIT to be tested>

Select (CL) the UNIT for which the test

routine is to be executed from 'Select Unit'.

When selecting each 'UNIT', go to 6. If 'ALL HDD' is selected, go to 9.

Copyright © 2010, Hitachi, Ltd.

6. <Select HDU Group to be tested>

Select (CL) the HDU Group for which the test routine is to be executed from 'UNIT'.

If [Select UNIT] is selected, go to 5.

Rev.0 / Sep.2010

#### **DIAG04-100**

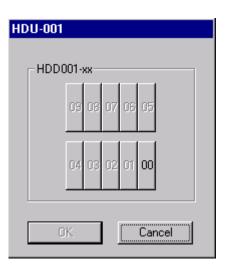

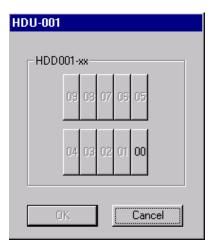

7. <Select HDD to be tested>

Select (CL) HDD for which the test routine is to be executed from selected HDU Group.

Then select (CL) the [OK] button.

Copyright © 2010, Hitachi, Ltd.

$8. \quad < Select [OK] > \\ Select (CL) the [OK] button.$

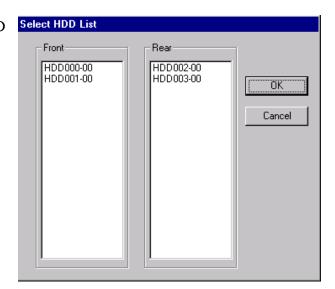

9. <Confirm HDD to be tested>

Confirm HDD to be tested in the 'Select HDD List'.

Then select (CL) [OK].

Rev.0 / Sep.2010

**DIAG04-110**

Copyright © 2010, Hitachi, Ltd.

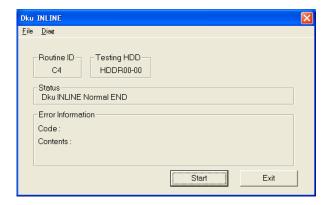

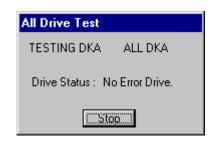

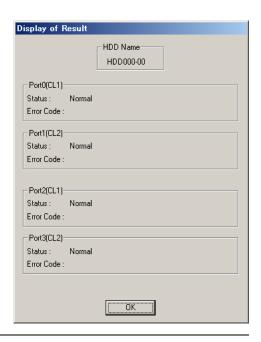

# 10. <Status Window>

The Status Window is displayed.

Normal end : Go to 11 Abnormal end : Go to 13

In case you abort the diagnosis, select (CL) the  $\,$

[Stop] button.

# 11. <DKU INLINE end>

After "Dku INLINE Normal END" is displayed in the Status field, select (CL) [Exit].

12. <Diagnosis end> Select (CL) [Exit].

Copyright © 2010, 2012, Hitachi, Ltd.

Hitachi Proprietary DKC710I

Rev.1 / Sep.2010, Oct.2012

#### **DIAG04-120**

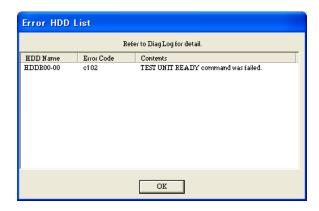

13. <Displaying 'Error HDD'> Error HDD List is displayed. Select (CL) [OK].

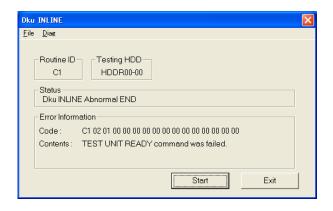

# 14. <Error End>

"Dku INLINE Abnormal END" is displayed in the Status field.

Refer to "2.2 Log indication" (SVP02-30). Select (CL) [Exit].

Go back to 12.

Rev.0 / Sep.2010

**DIAG04-130**

Copyright © 2010, Hitachi, Ltd.

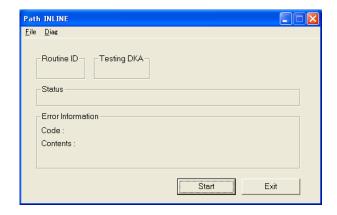

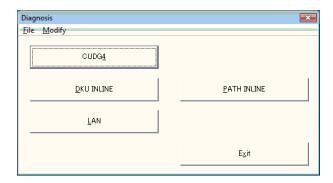

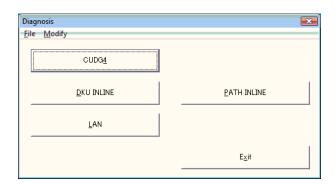

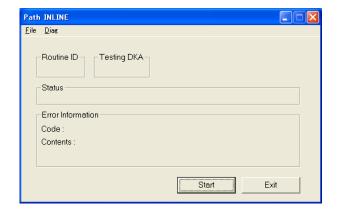

# **4.3 DKU PATH INLINE Test Procedures**

## 4.3.1 A0 routine Test Procedures

- 1. <Initial screen>

- <Operation mode change>

Change the mode to [Modify Mode].

Select (CL) [Diagnosis].

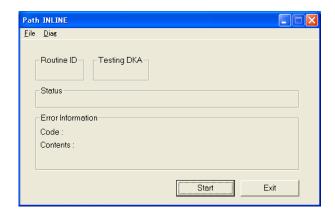

- 3. <Select 'PATH INLINE'>

The 'Diagnosis' window is displayed.

And select (CL) [PATH INLINE].

4. <Selecting [Start]> Select (CL) [Start].

Copyright © 2010, Hitachi, Ltd.

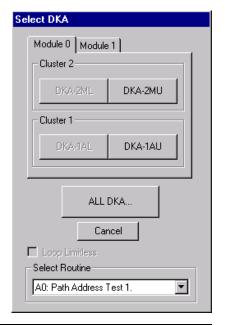

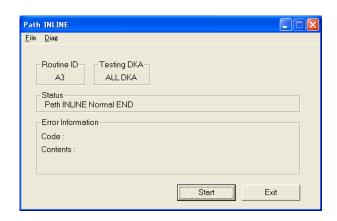

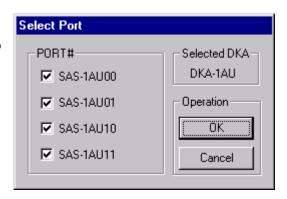

5. <Selecting Routine and the DKA>

Select the routine (A0) which is to be tested from "Select Routine", select (CL) the DKA for which the test routine is to be executed.

If the [ALL DKA...] button is selected: Go to 7.

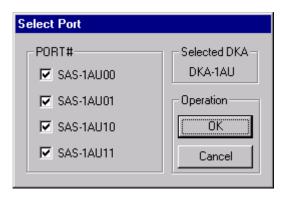

6. <Selecting the PORT to be diagnosed>

Select (CL) the PORT for which the test routine is to be executed. And select (CL) the [OK] button.

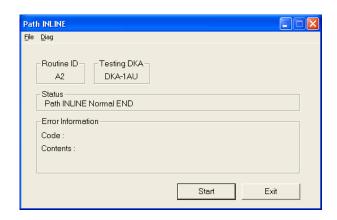

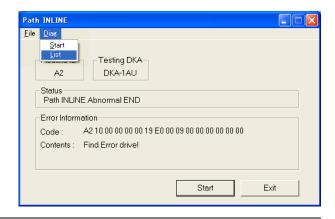

7. <Status Window>

The Status Window is displayed.

Normal end : Go to 8 Abnormal end : Go to 9

Rev.0 / Sep.2010

**DIAG04-150**

Copyright © 2010, Hitachi, Ltd.

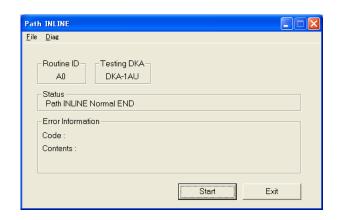

8. <Completing diagnosis>

After "Path INLINE Normal END" is displayed in the Status field, select (CL) [Exit].

Go to 13.

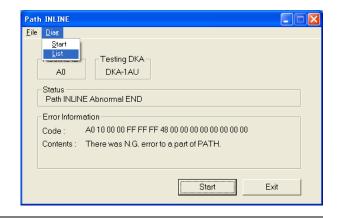

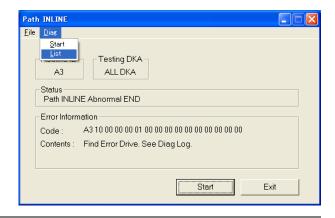

9. <Displaying the error detail> Select (DR) [List] from [Diag].

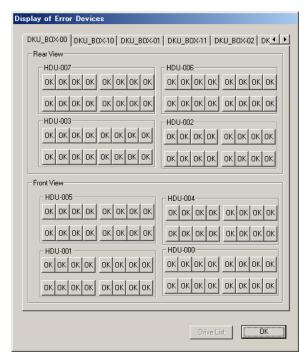

10. <Verification the incorrect part>

Select (CL) the incorrect part from [PORT].

When [PORT] is selected, go to 11. When [OK] is selected, go to 12.

If you want to display other UNIT, select (CL) [Unit Tab].

Rev.0 / Sep.2010

**DIAG04-160**

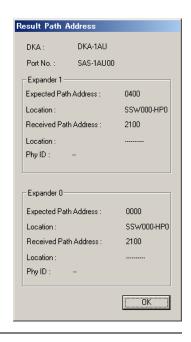

11. <Displaying 'Result'>

'Result' is selected.

Select (CL) the [OK] button.

Go to 10.

Copyright © 2010, Hitachi, Ltd.

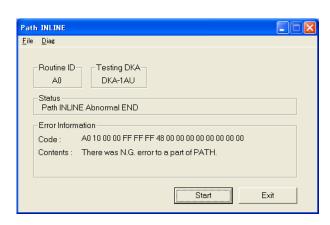

12. <DKU Path inline end>

After "Path INLINE Abnormal END" is displayed in the Status field, select (CL) [Exit].

13. <End of [Diagnosis]> Select (CL) [Exit].

Rev.0 / Sep.2010

**DIAG04-170**

Copyright © 2010, Hitachi, Ltd.

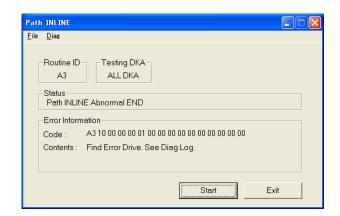

## 4.3.2 A3 routine Test Procedures

- 1. <Initial screen>

- <Operation mode change>

Change the mode to [Modify Mode].

Select (CL) [Diagnosis].

- 3. <Select 'PATH INLINE'>

The 'Diagnosis' window is displayed.

And select (CL) [PATH INLINE].

4. <Selecting [Start]> Select (CL) [Start].

#### **DIAG04-180**

# 5. <Selecting the DKA >

Select the routine (A3) which is to be tested from "Select Routine", Select (CL) the ALL DKA.

In case you loop the diagnosis, check the "Loop Limitless" Check-Box.

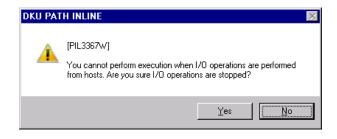

# 6. <I/O check>

An inquiry "You cannot perform execution when I/O operations are performed from hosts. Are you sure I/O operations are stopped?" is displayed.

It checks that I/O has stopped, then select (CL) the [Yes] button.

Performing this function without stopping I/O may block all of the LDEVs and lead to the system down. Verify the product serial number again. If the product serial number

is correct, you can continue the processing.

Do you want to continue?

DKU PATH INLINE

[PIL3366W]

# 7. <Execution check>

An inquiry "Performing this function without stopping I/O may block all of the LDEVs and lead to the system down.

Verify the product serial number again. If the product serial number is correct, you can continue the processing.

Do you want to continue?" is displayed.

Check the device manufacturer's serial

number to continue to select (CL) [Yes] if they are correct.

If different, the process is terminated select (CL) [No].

# 8. <Status Window>

The Status Window is displayed.

Normal end ----- Go to 9 Abnormal end ----- Go to 10

In case you abort the diagnosis, select (CL) the [Stop] button.

Yes

Νo

Rev.0 / Sep.2010

#### **DIAG04-190**

<DKU Path inline normal end>

After "Path INLINE NORMAL END" is displayed in the Status field, select (CL)

[Exit].

Go to 14.

Copyright © 2010, Hitachi, Ltd.

10. <Displaying the error detail> Select (DR) [List] from [Diag].

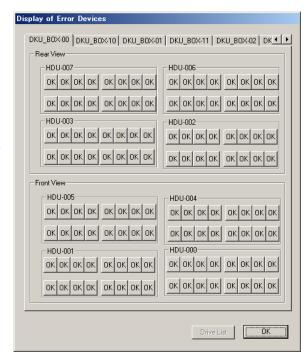

11. <Displaying the Error Devices>

"NG" is displayed in the PDEV installing position viewed in the R0-Unit.

If you want to display other Unit, select (CL) [Unit Tab].

If you want to refer to more detailed information about the "NG" PDEV, select the [NG] button. Go to 13.

"EQ" is displayed when the diagnosis ends on the way, and shows that equipped PDEV is undiagnosis.

Copyright © 2010, 2012, Hitachi, Ltd.

#### **DIAG04-200**

Hitachi Proprietary

12. <Displaying the Error detail>

Select (CL) the [OK] button after 'Result' is displayed.

13. <DKU Path inline end> Select (CL) [Exit].

Refer to "2.2 Log indication" (SVP02-30).

14. <End of [Diagnosis]> Select (CL) [Exit].

Rev.0 / Sep.2010

**DIAG04-210**

Copyright © 2010, Hitachi, Ltd.

# 4.3.3 A2 routine Test Procedures

1. <Initial screen>

<Operation mode change>

Change the mode to [Test Mode].

Select (CL) [Diagnosis].

Note: Please call Technical Support Division for asking how to change the mode to Test Mode.

3. <Select 'PATH INLINE'>

The 'Diagnosis' window is displayed.

And select (CL) [PATH INLINE].

4. <Selecting [Start]> Select (CL) [Start].

Rev.0 / Sep.2010

**DIAG04-220**

Copyright © 2010, Hitachi, Ltd.

5. <Selecting Routine and the DKA>

Select the routine (A2) which is to be tested from "Select

Routine", Select (CL) the DKA for which the test routine is to

be executed.

6. <Selecting the PORT to be diagnosed>

Selecting the PORT and the routine to be executed.

Select (CL) the PORT for which the test routine is to be executed. And select (CL) the [OK] button.

7. <Status Window>

The Status Window is displayed.

Normal end ----- Go to 8 Abnormal end ----- Go to 9

Rev.0 / Sep.2010

**DIAG04-230**

Copyright © 2010, Hitachi, Ltd.

8. <DKU Path INLINE normal end>

After "Path INLINE Normal END" is displayed in the Status field, select (CL) [Exit].

Go to 13.

9. <Displaying the error detail> Select (DR) [List] from [Diag].

10. <Displaying the Error Devices>

"NG" is displayed in the PDEV installing position viewed in the R0-Unit.

If you want to display other Unit, select (CL) [Unit Tab].

If you want to refer to more detailed information about the "NG" PDEV, select the "NG" button. Go to 11.

"EQ" is displayed when the diagnosis ends on the way, and shows that equipped PDEV is undiagnosis.

Copyright © 2010, Hitachi, Ltd.

#### **DIAG04-240**

11. <Displaying the Error detail>

Select (CL) the [OK] button after 'Result' is displayed.

12. <DKU Path inline end> Select (CL) [Exit].

13. <End of [Diagnosis]> Select (CL) [Exit].

Hitachi Proprietary DKC710I Rev.0 / Sep.2010 Copyright © 2010, Hitachi, Ltd.

**DIAG04-250**

Blank Sheet

Copyright © 2010, Hitachi, Ltd.

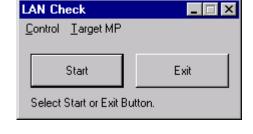

#### 4.4 LAN Check Procedure

- 1. <Initial screen>

- <Operation mode change>

Change the mode to [Modify mode].

Select (CL) [Diagnosis].

- <Activating LAN>

Select (CL) [LAN].

(The screen is changed to the LAN Check menu screen.)

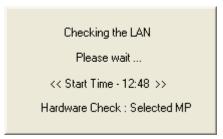

4. <Starting LAN Check> Select (CL) [Start] in the 'LAN Check' window.

<Supplementary explanation>

Although an installed processor is set to be default to execute a hardware diagnosis, all processors can be selected.

Installed processor : Select (CL) [Target MP] and

then select (DR) [Equipped MP].

All processors : Select (CL) [Target MP] and then select (DR) [All MP].

Rev.0 / Sep.2010

**DIAG04-270**

Copyright © 2010, Hitachi, Ltd.

# 5. < Displaying Wait message>

The Wait message is displayed. The screen will change to the result display screen in a few minutes.

# 6. < Displaying result>

# ① Adapter status display

When the Adapter button is selected, the screen is changed to the MP status screen.

The screen is returned to the LAN Check menu screen by selecting (CL) [OK].

# [Explanation on statuses]

The status is shown by the appearance of the button as follows:

Black : The test object is normal.

Blinking : The test object is abnormal.

Gray : The test object is not installed.

Rev.0 / Sep.2010

#### **DIAG04-280**

Copyright © 2010, Hitachi, Ltd.

## ② MP status display

When the MP button is selected, the screen is changed to the detailed status screen.

The screen is returned to the adapter status screen by selecting (CL) [OK].

## [Explanation on statuses]

The status is shown by the appearance of the MP button as follows:

Black : The concerning MP is normal.

Blinking: The test object is abnormal. However, for the MP which was

normal at the time of an FF-Ping,

"#" is indicated in front of the MP name.

Gray : The test object is not installed.

# [Supplemental explanation]

When the test object is not installed in the state that the hardware is abnormal:

The concerning MP is indicated in gray.

When the test object is not installed in the state that the hardware is normal:

The indication of the concerning MP is grayed and blinks.

When the test object is installed by an FF-Ping:

A character "#" is indicated in front of the MP name, and the name indication blinks.

When the test object is connected by an FF-Ping but not installed:

A character "#" is indicated in front of the MP name, and the name indication is grayed and blinks.

CHP00-1E

Rev.

Send Task

Copyright © 2010, Hitachi, Ltd.

R-Job

#### **DIAG04-290**

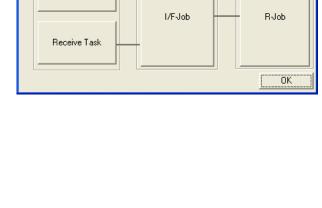

## 3 Detailed status display

Detailed information on the concerning MP is displayed.

The screen is returned to the MP status screen by selecting (CL) [OK].

## [Explanation on statuses]

The test result is shown by the appearance of the Task button as follows:

Black : The MP is normal from the

viewpoint of software.

Blinking: The blinking part has a problem.

Gray : Not diagnosed yet.

# [Supplemental explanation]

There are five types of status as shown below:

When the hardware is abnormal : Rcv., I/F-JOB, and R-JOB are indicated in gray. When the software is normal : Rcv., I/F-JOB, and R-JOB are indicated in black.

When the Rcv. is abnormal : Rcv. indication blinks, and I/F-JOB and R-JOB are indicated

in gray.

When the I/F-JOB is abnormal : Rcv. is indicated in black, I/F-JOB indication blinks, and R-

JOB is indicated in gray.

When the R-JOB is abnormal : Rcv. and I/F JOB are indicated in black and R-JOB

indication blinks.

# 7. <Exiting from LAN Check>

Select (CL) [Exit] in the 'LAN Check' window.

1/FJob

Rev.0 / Sep.2010 **DIAG05-10**  Copyright © 2010, Hitachi, Ltd.

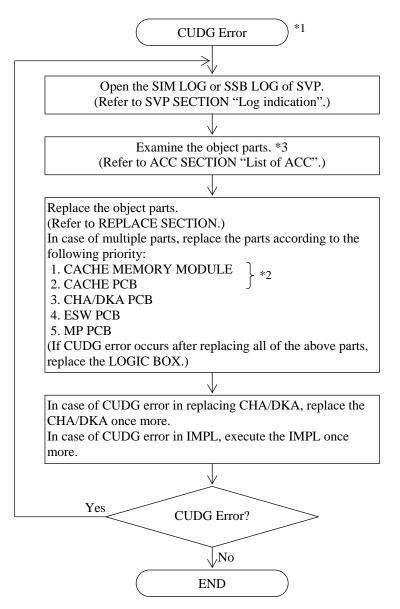

# 5. DIAG Trouble shooting

# **5.1 CUDG Trouble shooting**

Procedures of CUDG Trouble Shooting depend on CUDG Error Opportunity. The procedures are listed in Table 5.1-1 CUDG Trouble shooting Types.

Table 5.1-1 CUDG Trouble shooting Types

| CUDG Error Opportunity                    | CUDG Trouble shooting Types  | Procedure                  |

|-------------------------------------------|------------------------------|----------------------------|

| IMPL, CHA/DKA Replace,<br>CHA/DKA Install | CUDG3 Trouble shooting       | Following Subsection 5.1.1 |

| CUDG4                                     | CUDG4 Trouble shooting       | Following Subsection 5.1.2 |

| CACHE Replace,<br>CACHE Install           | INLINE CUDG Trouble shooting | Following Subsection 5.1.3 |

Note: If FPC is CACHE PCB or CACHE MEMORY MODULE, see Subsection 5.1.4 (DIAG05-60).

Rev.0 / Sep.2010

**DIAG05-20**

Copyright © 2010, Hitachi, Ltd.

# 5.1.1 CUDG3 Trouble shooting

- \*1: CUDG Error Code is SIM REFERENCE CODE = (7601xx) or SSB ERROR CODE = (3306).

- \*2: See Subsection 5.1.4 (DIAG05-60).

- \*3: Even if DKA (Disk Adapter PCB) is installed when the trouble of the Link error is detected by sharing CHA/DKA SLOT, "CHA-xxx" might be displayed in the Action Code (Location). When DKA is installed, Action Code (Location) is judged to be "DKA-xxx".

Rev.0 / Sep.2010

**DIAG05-30**

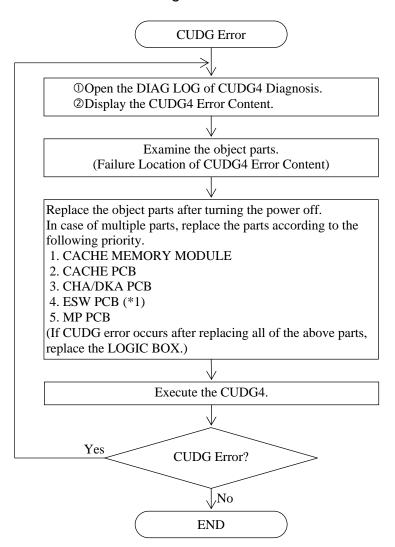

# 5.1.2 CUDG4 Trouble shooting

\*1: When ESW PK of module#0 and ESW PK of module#1 were displayed in Failure Location, Cables that connect module # 0 and module # 1 are exchanged before ESW PK is exchanged.

#### **DIAG05-40**

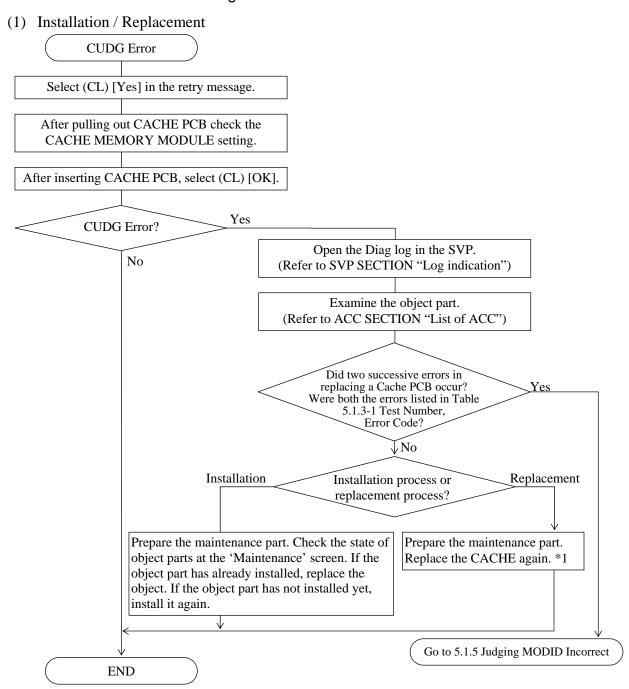

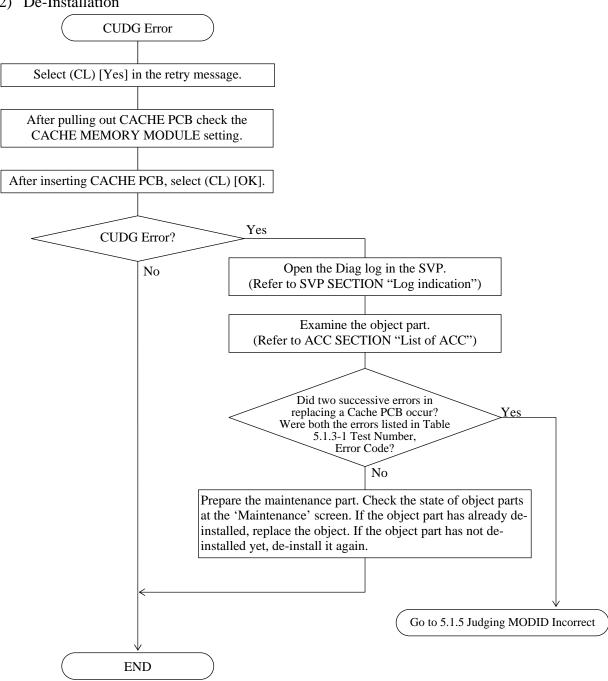

## 5.1.3 INLINE CUDG Trouble shooting

- \*1: In case of multiple parts, replace the parts according to the following priority:

- ① CACHE MEMORY MODULE

- ② CACHE PCB

- ③ CHA/DKA PCB

- **4** ESW PCB

- ⑤ MP PCB

(If a CUDG error occurred after replacing all of the above parts, replace LOGIC BOX.) If the error part is CACHE MEMORY MODULE/CACHE PCB, refer to Subsection 5.1.4 (DIAG05-60).

## (2) De-Installation

Table 5.1.3-1 Generated by MODID fraud Test Number, Error Code

| Test Number | Error Code |

|-------------|------------|

| 012a        | 2000       |

| 012c        | 2000       |

| 012c        | 0001       |

Copyright © 2010, Hitachi, Ltd.

#### **DIAG05-60**

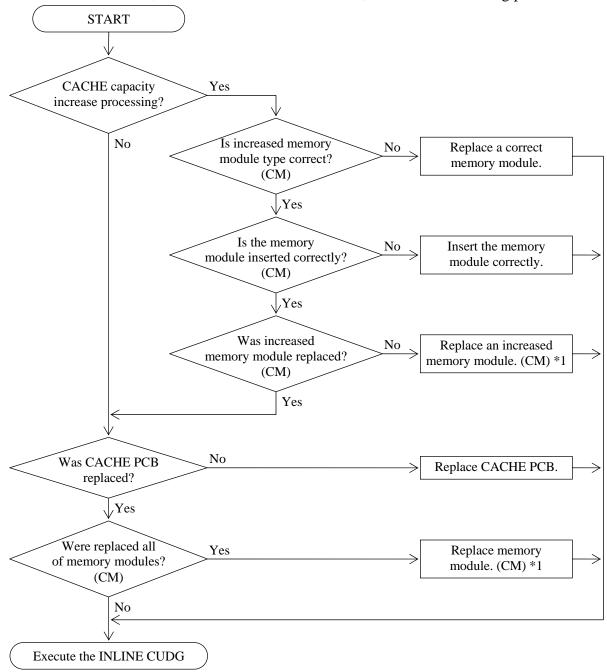

# 5.1.4 CACHE PCB, CACHE MEMORY MODULE Trouble shooting

If FPC is CACHE PCB, CACHE MEMORY MODULE, execute the following process.

\*1: In case of multiple module groups, replace the module groups one by one.

If a CUDG error occurs after replacing the group, put them to original position.

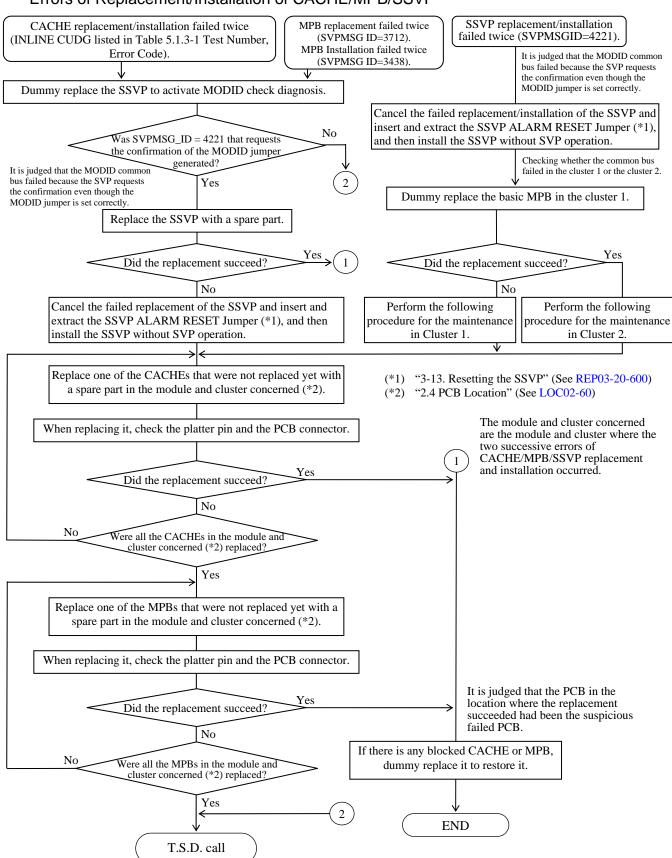

# 5.1.5 Judgement of MODID Incorrectness and Recovery Procedure in Case of Two Successive Errors of Replacement/Installation of CACHE/MPB/SSVP

Rev.0 / Sep.2010

Copyright © 2010, Hitachi, Ltd. **DIAG05-70**

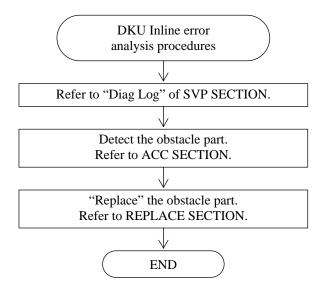

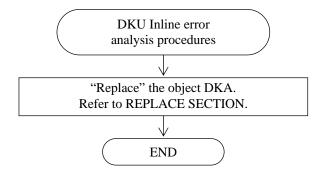

# **5.2 DKU INLINE Trouble shooting**

Trouble shoot procedures (Except Error Code = "xx e3" / "xx e4")

Trouble shoot procedures (In case of Error Code = "xx e3" / "xx e4")

Rev.0 / Sep.2010

Copyright © 2010, Hitachi, Ltd. **DIAG05-80**

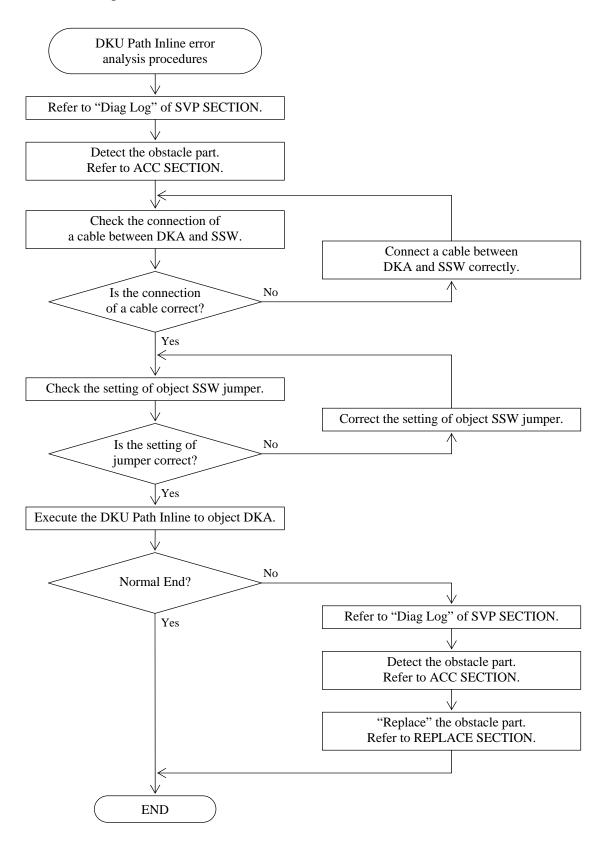

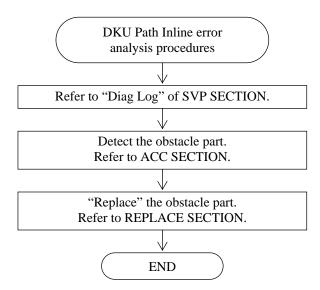

# 5.3 DKU PATH INLINE Trouble shooting

Trouble shoot procedures (Error Code = "ax ad", "ax ae", "ax 07")

Rev.0 / Sep.2010

**DIAG05-90**

Copyright © 2010, Hitachi, Ltd.

Trouble shoot procedures (Except Error Code = "ax ad", "ax ae", "ax 07")

Rev.0 / Sep.2010

**DIAG06-10**

# 6. DIAG Errors

# **6.1 DKU INLINE Error Code List**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte.

|    | Error Byte |    |    |    |    |    |    |    |    |                                                 |

|----|------------|----|----|----|----|----|----|----|----|-------------------------------------------------|

| 01 | 02         | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | Contents                                        |

| XX | 51         |    |    |    |    |    |    |    |    | The Svp_InitMultiChain function failed.         |

| XX | 52         |    |    |    |    |    |    |    |    | The Svp_RegistMultiChain function failed.       |

| XX | 53         |    |    |    |    |    |    |    |    | The Svp_ExecMultChainedDkcFunc function failed. |

| XX | 54         |    |    |    |    |    |    |    |    | The Svp_GetMultiChain function failed.          |

| XX | 55         |    |    |    |    |    |    |    |    |                                                 |

| XX | 56         |    |    |    |    |    |    |    |    |                                                 |

| XX | 57         |    |    |    |    |    |    |    |    |                                                 |

| XX | 58         |    |    |    |    |    |    |    |    |                                                 |

| XX | 59         |    |    |    |    |    |    |    |    |                                                 |

| XX | 5A         |    |    |    |    |    |    |    |    |                                                 |

| XX | 5B         |    |    |    |    |    |    |    |    |                                                 |

| XX | 5C         |    |    |    |    |    |    |    |    |                                                 |

| XX | 5D         |    |    |    |    |    |    |    |    |                                                 |

| XX | 5E         |    |    |    |    |    |    |    |    |                                                 |

|    |            |    |    |    |    |    |    |    |    |                                                 |

## **DIAG06-20**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte.

|    | Error Byte |    |    |    |    |    |    |    |    |                                                    |

|----|------------|----|----|----|----|----|----|----|----|----------------------------------------------------|

| 01 | 02         | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | Contents                                           |

| XX | E0         |    |    |    |    |    |    |    |    | The TEST UNIT READY command failed.                |

| XX | E1         |    |    |    |    |    |    |    |    | The Bypass Check command failed.                   |

| XX | E2         |    |    |    |    |    |    |    |    | The Reset Bypass command failed.                   |

| XX | E3         |    |    |    |    |    |    |    |    | Communication of between DKC and SVP was TIME OUT. |

| XX | E4         |    |    |    |    |    |    |    |    | Communication failed.                              |

| XX | E5         |    |    |    |    |    |    |    |    | Not Used                                           |

| XX | E6         |    |    |    |    |    |    |    |    | Not Used                                           |

|    |            |    |    |    |    |    |    |    |    |                                                    |

| XX | E8         |    |    |    |    |    |    |    |    | The Start INLINE command was failed.               |

| XX | E9         |    |    |    |    |    |    |    |    | The End INLINE command failed.                     |

| XX | EA         |    |    |    |    |    |    |    |    | The specified HDD does not exist.                  |

| XX | EB         |    |    |    |    |    |    |    |    | SVP error (Program Error)                          |

| XX | EC         |    |    |    |    |    |    |    |    | Windows error                                      |

| XX | ED         |    |    |    |    |    |    |    |    | SVP error (DKC-SVP Communication)                  |

|    |            |    |    |    |    |    |    |    |    |                                                    |

Rev.0 / Sep.2010

**DIAG06-30**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte. Refer to DIAG06-10, when there is nothing to the following error code tables.

|    |    |    |    | Error | Byte | ;  |    |    |    |                                                      |

|----|----|----|----|-------|------|----|----|----|----|------------------------------------------------------|

| 01 | 02 | 03 | 04 | 05    | 06   | 07 | 08 | 09 | 10 | Contents                                             |

| C1 | 01 |    |    |       |      |    |    |    |    | Communication of the TEST UNIT READY command failed. |

| C1 | 02 |    |    |       |      |    |    |    |    | The TEST UNIT READY command failed.                  |

| C1 | 03 |    |    |       |      |    |    |    |    | Communication of the REQUEST SENSE command failed.   |

| C1 | 04 |    |    |       |      |    |    |    |    | The REQUEST SENSE command failed.                    |

| C1 | 05 |    |    |       |      |    |    |    |    | The SENSE KEY is abnormal.                           |

| C1 | 06 |    |    |       |      |    |    |    |    | The SENSE CODE is abnormal.                          |

| C1 | 07 |    |    |       |      |    |    |    |    | The ADDITIONAL CODE is abnormal.                     |

|    |    |    |    |       |      |    |    |    |    |                                                      |

|    |    |    |    |       |      |    |    |    |    |                                                      |

|    |    |    |    |       |      |    |    |    |    |                                                      |

|    |    |    |    |       |      |    |    |    |    |                                                      |

|    |    |    |    |       |      |    |    |    |    |                                                      |

|    |    |    |    |       |      |    |    |    |    |                                                      |

|    |    |    |    |       |      |    |    |    |    |                                                      |

|    |    |    |    |       |      |    |    |    |    |                                                      |

Rev.0 / Sep.2010

**DIAG06-40**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte. Refer to DIAG06-10, when there is nothing to the following error code tables.

|    | Error Byte |    |    |    |    |    |    |    |    |                                              |

|----|------------|----|----|----|----|----|----|----|----|----------------------------------------------|

| 01 | 02         | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | Contents                                     |

| C2 | 01         |    |    |    |    |    |    |    |    | Communication of the INQUIRY command failed. |

| C2 | 02         |    |    |    |    |    |    |    |    | The INQUIRY command failed.                  |

| C2 | 03         |    |    |    |    |    |    |    |    | The Vendor ID is abnormal.                   |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

|    |            |    |    |    |    |    |    |    |    |                                              |

Rev.0 / Sep.2010

**DIAG06-50**

Copyright © 2010, Hitachi, Ltd.

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte. Refer to DIAG06-10, when there is nothing to the following error code tables.

|    | Error Byte |    |    |    |    |    |    |    |    |                                                      |

|----|------------|----|----|----|----|----|----|----|----|------------------------------------------------------|

| 01 | 02         | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | Contents                                             |

| C3 | 01         |    |    |    |    |    |    |    |    | Communication of the STOP UNIT command failed.       |

| C3 | 02         |    |    |    |    |    |    |    |    | The STOP UNIT command failed.                        |

| C3 | 03         |    |    |    |    |    |    |    |    | The Delay function failed.                           |

| C3 | 04         |    |    |    |    |    |    |    |    | Communication of the START UNIT command failed.      |

| C3 | 05         |    |    |    |    |    |    |    |    | The START UNIT command failed.                       |

| C3 | 06         |    |    |    |    |    |    |    |    | Communication of the TEST UNIT READY command failed. |

| C3 | 07         |    |    |    |    |    |    |    |    | The TEST UNIT READY command failed.                  |

| C3 | 08         |    |    |    |    |    |    |    |    | Communication of the REQUEST SENSE command failed.   |

| C3 | 09         |    |    |    |    |    |    |    |    | The REQUEST SENSE command failed.                    |

| C3 | 0A         |    |    |    |    |    |    |    |    | The SENSE KEY is abnormal.                           |

| C3 | 0B         |    |    |    |    |    |    |    |    | The SENSE CODE is abnormal.                          |

| C3 | 0C         |    |    |    |    |    |    |    |    | The ADDITIONAL CODE is abnormal.                     |

|    |            |    |    |    |    |    |    |    |    |                                                      |

|    |            |    |    |    |    |    |    |    |    |                                                      |

|    |            |    |    |    |    |    |    |    |    |                                                      |

Rev.0 / Sep.2010

**DIAG06-60**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte. Refer to DIAG06-10, when there is nothing to the following error code tables.

|    | Error Byte |    |    |    |    |    |    |    |    |                                                |

|----|------------|----|----|----|----|----|----|----|----|------------------------------------------------|

| 01 | 02         | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | Contents                                       |

| C4 | 01         |    |    |    |    |    |    |    |    | Communication of the SELF TEST command failed. |

| C4 | 02         |    |    |    |    |    |    |    |    | The SELF TEST command failed.                  |

| C4 | 03         |    |    |    |    |    |    |    |    | The SELF TEST failed.                          |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

|    |            |    |    |    |    |    |    |    |    |                                                |

Rev.0 / Sep.2010

**DIAG06-70**

# **6.2 PATH INLINE Error Code List**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte.

|    |    |    |    | Error | Byte |    |    |    |    |                                                                                                |

|----|----|----|----|-------|------|----|----|----|----|------------------------------------------------------------------------------------------------|

| 01 | 02 | 03 | 04 | 05    | 06   | 07 | 08 | 09 | 10 | Contents                                                                                       |

| XX | 51 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 52 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 53 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 54 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 55 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 56 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 57 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 58 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 59 |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 5A |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 5B |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 5C |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 5D |    |    |       |      |    |    |    |    |                                                                                                |

| XX | 5E |    |    |       |      |    |    |    |    | SSW that doesn't exist in configuration information is equipped. Please confirm equipping SSW. |

|    |    |    |    |       |      |    |    |    |    |                                                                                                |

Rev.1 / Sep.2010, Oct.2012

#### **DIAG06-80**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte.

|    |    |    |    |    |    |    |      | Error | Byte | ;  |      |    |    |    |    |    |    |                                                              |

|----|----|----|----|----|----|----|------|-------|------|----|------|----|----|----|----|----|----|--------------------------------------------------------------|

| 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08   | 09    | 10   | 11 | 12   | 13 | 14 | 15 | 16 | 17 | 18 | Contents                                                     |

| XX | A1 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A2 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A3 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A4 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A5 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A6 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A7 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A8 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | A9 |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

| XX | AA | D# | P# | U# |    |    |      |       |      |    |      |    |    |    |    |    |    | SSW Error                                                    |

| XX | AB | D# | P# | U# |    |    |      |       |      |    |      |    |    | Е  | V  | R  | V  | Invalid Phy ID                                               |

| XX | AC |    |    |    |    |    |      |       |      | EV | (*2) | R  | V  |    |    |    |    | Invalid SAS address data. (*3)                               |

| XX | AD |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    | Invalid SAS address data. (*3)<br>(Refer to AxAE for detail) |

| XX | AE | D# | P# | U# |    | EV | (*2) | R     | V    |    |      |    |    |    |    |    |    | Invalid SAS address data. (*3)                               |

| XX | BC | D# | P# | U# |    |    |      |       |      |    |      |    |    |    |    |    |    | Invalid connecting DKU Type.                                 |

| XX | BE | D# | P# | U# |    |    |      |       |      |    |      |    |    |    |    |    |    | Invalid own DKU Type.                                        |

|    |    |    |    |    |    |    |      |       |      |    |      |    |    |    |    |    |    |                                                              |

<sup>\*2:</sup> Refer to SAS Address mapping (DIAG06-210, 220) for Expected Value.

<sup>\*3:</sup> There is the possibility of a SAS cable connection mistake or a jumper setting mistake of SSW. Refer to LOCATION SECTION (LOC06-50) for the setting of the jumper socket and switch.

## **DIAG06-81**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte.

|    |    |    |    | Error | Byte | ;  |    |    |    |                                                    |

|----|----|----|----|-------|------|----|----|----|----|----------------------------------------------------|

| 01 | 02 | 03 | 04 | 05    | 06   | 07 | 08 | 09 | 10 | Contents                                           |

| XX | E1 |    |    |       |      |    |    |    |    | The Bypass Check command failed.                   |

| XX | E2 |    |    |       |      |    |    |    |    | The Reset Bypass command failed.                   |

| XX | E3 |    |    |       |      |    |    |    |    | Communication of between DKC and SVP was TIME OUT. |

| XX | E4 |    |    |       |      |    |    |    |    | Communication failed.                              |

| XX | E5 |    |    |       |      |    |    |    |    | The LIP command failed.                            |

| XX | E6 |    |    |       |      |    |    |    |    | The Set Bypass command failed.                     |

|    |    |    |    |       |      |    |    |    |    |                                                    |

| XX | E8 |    |    |       |      |    |    |    |    | The Start INLINE command failed.                   |

| XX | E9 |    |    |       |      |    |    |    |    | The End INLINE command failed.                     |

| XX | EA |    |    |       |      |    |    |    |    | The specified HDD does not exist.                  |

| XX | EB |    |    |       |      |    |    |    |    | SVP error (Program Error)                          |

| XX | EC |    |    |       |      |    |    |    |    | Windows error                                      |

| XX | ED |    |    |       |      |    |    |    |    | SVP error (DKC-SVP Communication)                  |

|    |    |    |    |       |      |    |    |    |    |                                                    |

|    |    |    |    |       |      |    |    |    |    |                                                    |

## Rev.0 / Sep.2010 **DIAG06-90**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte.

|    | Error Byte |    |    |    |    |    |    |    |    |                                                                                       |

|----|------------|----|----|----|----|----|----|----|----|---------------------------------------------------------------------------------------|

| 01 | 02         | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | Contents                                                                              |

| XX | F9         |    |    |    |    |    |    |    |    | The PDEV disorder detection                                                           |

| XX | FA         |    |    |    |    |    |    |    |    | The SVR disorder detection                                                            |

| XX | FB         |    |    |    |    |    |    |    |    | The SVR-EX disorder detection                                                         |

| XX | FC         | D# | P# | U# |    |    |    |    |    | FC cable connection error. There is the possibility of a FC cable connection mistake. |

| XX | FE         |    |    |    |    |    |    |    |    | FC Check error. There is the possibility of a FC cable connection mistake.            |

|    |            |    |    |    |    |    |    |    |    |                                                                                       |

|    |            |    |    |    |    |    |    |    |    |                                                                                       |

|    |            |    |    |    |    |    |    |    |    |                                                                                       |

|    |            |    |    |    |    |    |    |    |    |                                                                                       |

<u>D#:DKA# P#:PORT# U#:UNIT#</u>

(\*1)

Rev.0 / Sep.2010

**DIAG06-100**

\*1: DKA#, PORT#, UNIT# mapping

| 1. DIXIII, I OIXIII, OIX         | 11 0                                                                                |                                                                                              |

|----------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| DKA#: 0-3                        | PORT#: 0-3                                                                          | UNIT#: 0-7                                                                                   |

| 0: DKA-1AU                       | 0: HDU-000, 004 ~ 070,074                                                           | 0: DKUBOX-00                                                                                 |

|                                  | 1: HDU-001, 005 ~ 071,075                                                           | 1: DKUBOX-01                                                                                 |

| 1: DKA-1AL                       | 2: HDU-002, 006 ~ 072,076                                                           | 2: DKUBOX-02                                                                                 |

|                                  | 3: HDU-003, 007 ~ 073,077                                                           | 3: DKUBOX-03                                                                                 |

| 2: DKA-2MU                       |                                                                                     | 4: DKUBOX-04                                                                                 |

| 2. 5101 2110                     |                                                                                     | 5: DKUBOX-05                                                                                 |

| 3: DKA-2ML                       |                                                                                     | 6: DKUBOX-06                                                                                 |

| J. DKA-ZWIL                      |                                                                                     | 7: DKUBOX-07                                                                                 |

|                                  |                                                                                     |                                                                                              |

| DKA#: 4-7                        | PORT#: 0-3                                                                          | UNIT#: 0-7                                                                                   |

| DKA#: 4-7<br>4: DKA-1LU          | PORT#: 0-3<br>0: HDU-100, 104 ~ 170,174                                             | UNIT#: 0-7<br>0: DKUBOX-10                                                                   |

|                                  |                                                                                     |                                                                                              |

|                                  | 0: HDU-100, 104 ~ 170,174                                                           | 0: DKUBOX-10                                                                                 |

| 4: DKA-1LU                       | 0: HDU-100, 104 ~ 170,174<br>1: HDU-101, 105 ~ 171,175                              | 0: DKUBOX-10<br>1: DKUBOX-11                                                                 |

| 4: DKA-1LU<br>5: DKA-1LL         | 0: HDU-100, 104 ~ 170,174<br>1: HDU-101, 105 ~ 171,175<br>2: HDU-102, 106 ~ 172,176 | 0: DKUBOX-10<br>1: DKUBOX-11<br>2: DKUBOX-12                                                 |

| 4: DKA-1LU                       | 0: HDU-100, 104 ~ 170,174<br>1: HDU-101, 105 ~ 171,175<br>2: HDU-102, 106 ~ 172,176 | 0: DKUBOX-10<br>1: DKUBOX-11<br>2: DKUBOX-12<br>3: DKUBOX-13                                 |

| 4: DKA-1LU 5: DKA-1LL 6: DKA-2XU | 0: HDU-100, 104 ~ 170,174<br>1: HDU-101, 105 ~ 171,175<br>2: HDU-102, 106 ~ 172,176 | 0: DKUBOX-10<br>1: DKUBOX-11<br>2: DKUBOX-12<br>3: DKUBOX-13<br>4: DKUBOX-14                 |

| 4: DKA-1LU<br>5: DKA-1LL         | 0: HDU-100, 104 ~ 170,174<br>1: HDU-101, 105 ~ 171,175<br>2: HDU-102, 106 ~ 172,176 | 0: DKUBOX-10<br>1: DKUBOX-11<br>2: DKUBOX-12<br>3: DKUBOX-13<br>4: DKUBOX-14<br>5: DKUBOX-15 |

Rev.3 / Mar.2011, May.2012

Copyright © 2010, 2012, Hitachi, Ltd.

**DIAG06-110**

Notes: Replace Error Code on Diagnosis Log of SVP Information since the 8th Byte and after of the Detail Information Byte correspond to Byte 01 and after of Error Byte. Refer to from DIAG06-70 to DIAG06-100, when there is nothing to the following error code tables.

|    |    |    |     | Er  | ror By | yte |     |     |     |     |                                                                           |

|----|----|----|-----|-----|--------|-----|-----|-----|-----|-----|---------------------------------------------------------------------------|

| 01 | 02 | 03 | 04  | 05  | 06     | 07  | 08  | 09  | 10  | 11  | Contents                                                                  |

| A0 | 01 |    |     |     |        |     |     |     |     |     | The Reset Bypass command failed.                                          |

| A0 | 02 |    |     |     |        |     |     |     |     |     | The Bypass check command failed.                                          |

| A0 | 03 |    |     |     |        |     |     |     |     |     | Communication of the INQUIRY command failed.                              |

| A0 | 04 |    |     |     |        |     |     |     |     |     | The INQUIRY information failed.                                           |

| A0 | 05 |    |     |     |        |     |     |     |     |     | The INQUIRY command failed.                                               |

| A0 | 06 |    |     |     |        |     |     |     |     |     | The Vender ID doesn't match.                                              |

| A0 | 07 |    |     |     |        |     |     |     |     |     | PORT mistake. There is the possibility of a SAS cable connection mistake. |

| A0 | 0B |    |     |     |        |     |     |     |     |     | Bypass check error                                                        |

|    |    |    |     |     |        |     |     |     |     |     |                                                                           |

| A0 | 1X | D# | POS | P1S | P2S    | P3S | P4S | P5S | P6S | P7S | Obstruction occurred in a part of the PATH.                               |

| A0 | 2X | D# | POS | P1S | P2S    | P3S | P4S | P5S | P6S | P7S | Obstruction occurred in all the PATH.                                     |

| A0 | AA | D# | P#  | U#  |        |     |     |     |     |     | SSW Error                                                                 |

| A0 | AB | D# | P#  | U#  |        |     |     |     |     |     | Invalid Phy ID                                                            |

|    |    |    |     |     |        |     |     |     |     |     |                                                                           |

| A0 | AD |    |     |     |        |     |     |     |     |     | Invalid SAS address data. (*3) (Refer to A0AE for detail)                 |

| A0 | AE | D# | P#  | U#  |        |     |     |     |     |     | Invalid SAS address data. (*3)                                            |

|    |    |    |     |     |        |     |     |     |     |     |                                                                           |

| A0 | BC | D# | P#  | U#  |        |     |     |     |     |     | Invalid connecting DKU Type.                                              |

| A0 | BE | D# | P#  | U#  |        |     |     |     |     |     | Invalid own DKU Type.                                                     |

|    |    |    |     |     |        |     |     |     |     |     |                                                                           |

D#: DKA# P#: PORT# U#: UNIT# EV: Expected Value

RV : Received Value P(0-7)S : PORT#(0-7) report (FF : Normal, Not FF : Abnormal)

(\*1)

\*1: DKA#, PORT#, UNIT# mapping