# F-7C AND F-7E PROCESSOR GROUP FUNCTIONAL CHARACTERISTICS

# **Statement on EN55022 Compliance**

**WARNING:** This is a Class A product. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.

# **Statement on Federal Communications Commission (FCC) Compliance**

**NOTE:** This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his/her own expense. The user is cautioned that changes or modifications not expressly approved by the manufacturer could void the user's authority to operate the equipment.

#### **Trademarks**

AIX, AIX/ESA, CICS/ESA, DB2, Enterprise Systems Architecture/390, Enterprise Systems Connection Architecture, ESCON, IBM, IMS/ESA, OS/390, Parallel Sysplex, S/390, Sysplex Timer, System/390, and VM/ESA are registered trademarks of International Business Machines Corporation. DFSORT, ESA/390, MVS/ESA, MVS/SP, MVS/XA, RMF, S/370, and System/370 are trademarks of International Business Machines Corporation.

All Rights Reserved, Copyright © 1998, 1999, Hitachi, Ltd.

#### F7-GA-1C01 Third Edition (March 1999)

This edition obsoletes F7-GA-1C01 second edition. Although this second edition provides the latest information available, such information is subject to change without prior notice. The reader is responsible for maintaining up-to-date editions.

# **Change Record**

| Revision No. | Date              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Affected Pages |

|--------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 0            | September<br>1998 | Original Edition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| 1            | December<br>1998  | <ul> <li>Second Edition</li> <li>Additions and changes associated with introduction of F-7C Turbo Models.</li> <li>Changes associated with introduction of 31CD, 52CD, and B2C Base Models, and 0XC (B2C) CF Model.</li> <li>Changes associated with new CHPID assignments.</li> <li>Changes in increments of MS and ES.</li> <li>Addition of note on available channel numbers.</li> <li>Changes in external views of F-7C models.</li> <li>Changes in F-7C basic logical components.</li> <li>Editorial changes.</li> </ul> | All.           |

| 2            | March 1999        | <ul> <li>Third Edition</li> <li>Additions and changes associated with introduction of F-7E Turbo Models.</li> <li>Addition of information relating to Integrated Disk.</li> <li>Addition of information on Virtual Server Phase-1.</li> </ul>                                                                                                                                                                                                                                                                                 | All.           |

# **PREFACE**

This document serves as a functional characteristics manual draft for the F-7C and F-7E Processor Group.

For the purpose of generating a user manual, Hitachi, Ltd. allows the OEM customers to reproduce, rewrite, modify and edit all or part of this document for their use for the assumed OEM marketing/sales of the F-7C and F-7E Processor Group while retaining copyright and all rights associated with copyright.

This document describes primarily the functional characteristics and configuration of the F-7C and F-7E Processor Group hardware, without particular regard to how it is utilized by software. It should be understood, therefore, that not all the hardware capabilities may be supported by the target systems. It should be also noted that the breakdown models given here do not necessarily match the models defined for ordering in the OEM Sales Agreement; for example, models transparent to the end users are omitted, renamed or treated as included in appropriate host features.

Information contained in this document is subject to change without notice.

# Reference manuals

- F-7C and F-7E Processor Group Installation Planning Guide (F7-GA-1C02)

- Hitachi MLPF 3.3.3 User Manual (HT-GA-1012)

- Hitachi MLPF 3.5.0 User Manual (HT-GA-1015)

- Hitachi HCCFA 1.0–3.1 User Manual (HT-GA-1020)

- Hitachi HCCFA 4.0 User Manual (HT-GA-1025)

- IBM System/360 and System/370 I/O Interface Channel to Control Unit Original Equipment Manufacturers' Information (GA22-6974)

- IBM System/370 Extended Architecture Principles of Operation (SA22-7085)

- IBM System/370 Extended Architecture Interpretive Execution (SA22-7095)

- IBM Enterprise Systems Architecture/390 Principles of Operation (SA22-7201)

- IBM Enterprise Systems Architecture/390 ESCON I/O Interface (SA22-7202)

- IBM Enterprise Systems Architecture/390 ESCON Channel to Channel Adapter (SA22-7203)

- IBM Enterprise Systems Architecture/390 Common I/O Device Commands (SA22-7204)

- IBM ES/9000 Input/Output Configuration Program User's Guide and ESCON Channel-to-Channel Reference (GC38-0401)

# TABLE OF CONTENTS

|                                                               |      | 1.7.4 Parallel Sysplex Computing                             | 1-13 |

|---------------------------------------------------------------|------|--------------------------------------------------------------|------|

|                                                               |      | 1.7.5 LPAR Support                                           |      |

| PREFACE                                                       | III  | 1.7.6 Virtual Server Facility Phase-1                        |      |

| 11011102                                                      |      | 1.7.7 ESCON Channel Compatibility                            |      |

| LIST OF FIGURES                                               | VI   | 1.7.8 Parallel Channel Support                               |      |

| ZIST OT TIGORES                                               | , 1  | 1.7.9 Open Systems Connection Feature                        |      |

| LIST OF TABLES                                                | VI   | 1.7.10 Console Support Including GUI and Security            |      |

|                                                               |      | 1.7.11 RAS Approach to Non-Stop Computing                    |      |

| LIST OF ABBREVIATIONS                                         | VII  |                                                              |      |

|                                                               |      | CHAPTER 2 INSTRUCTION PROCESSOR AND SYSTEM PROCESSOR         |      |

| CHAPTER 1 F-7C AND F-7E PROCESSOR GROUP OVERVIEW              |      |                                                              |      |

|                                                               |      | 2.1 Processor Overview                                       |      |

| 1.1 Introduction                                              | 1-1  | 2.2 System Processor Interface Design and Function           |      |

| 1.2 Model Grouping                                            | 1-1  | 2.2.1 Interface between SP and IP                            |      |

| 1.3 Benefits                                                  | 1-3  | 2.2.2 SVP Interface                                          |      |

| 1.3.1 Leading-Edge Technologies                               | 1-3  | 2.2.3 IOP Interface                                          |      |

| 1.3.2 Excellent Performance Efficiencies                      | 1-3  | 2.3 Address Translation Process with Lookaside Buffers       | 2-2  |

| 1.3.3 Full Compatibility                                      | 1-4  | 2.3.1 Virtual Address Formats                                | 2-2  |

| 1.3.4 Balanced Scalability                                    | 1-4  | 2.3.2 Address Translation Using Translation Lookaside Buffer | 2-2  |

| 1.3.5 Optimized Reliability, Availability, and Serviceability | 1-4  | 2.3.3 Address Translation Using Access Register              | 2-3  |

| 1.4 Physical Design Highlights                                | 1-4  | 2.4 Pipeline Design and Features                             |      |

| 1.5 Configuration                                             |      | 2.5 Alternate Processors                                     | 2-4  |

| 1.5.1 Instruction Processor and System Processor              | 1-9  |                                                              |      |

| 1.5.2 System Controller and Processor Storage                 | 1-9  |                                                              |      |

| 1.5.3 Input/Output Device Management                          | 1-9  | CHAPTER 3 STORAGE SUBSYSTEM                                  |      |

| 1.5.4 SVP/CD Subsystem                                        | 1-10 |                                                              |      |

| 1.5.5 Optional Components                                     |      | 3.1 Storage Subsystem Overview                               | 3-1  |

| 1.5.6 Processor Configuration Summary                         | 1-10 | 3.2 Hardware Organization                                    | 3-1  |

| 1.6 System Design Highlights                                  | 1-10 | 3.3 Cache Buffers                                            | 3-2  |

| 1.6.1 Operating System Support                                |      | 3.3.1 Buffer Storage (BS)                                    | 3-2  |

| 1.6.2 Advanced Logic Design                                   |      | 3.3.2 Work Storage (WS)                                      | 3-2  |

| 1.6.3 CPU ID                                                  | 1-11 | 3.3.3 Cache Algorithms and Data Movement                     | 3-2  |

| 1.6.4 Packaging Technology                                    |      | 3.4 System Controller                                        | 3-3  |

| 1.7 Functional Design Highlights                              |      |                                                              |      |

| 1.7.1 ESA/390 Architecture Support                            |      |                                                              |      |

| 1.7.2 S/390 Architectural Features and Functions              |      |                                                              |      |

| 3.5 Processor Storage                                   | 3-3 | 5.3 CD Hardware Design and Features                              | 5-3 |

|---------------------------------------------------------|-----|------------------------------------------------------------------|-----|

| 3.5.1 Main Storage                                      | 3-3 | 5.3.1 CD Hardware Design                                         | 5-3 |

| 3.5.2 Expanded Storage                                  | 3-4 | 5.3.2 CD Operating Modes                                         |     |

| 3.5.3 Processor Storage Sizes                           |     | 5.3.3 CD Features                                                |     |

| 3.6 Storage Protection                                  | 3-5 | 5.4 User Access Levels (Security) and Operating Mode Definitions | 5-5 |

| 3.6.1 Key-Controlled Protection                         |     | 5.4.1 Operator (Op)—MCD Mode                                     |     |

| 3.6.2 Low-Address Protection                            |     | 5.4.2 Advanced Operator (AO)—MCD Mode                            |     |

| 3.6.3 Page Protection                                   | 3-5 | 5.4.3 System Programmer (SP)—MCD Mode                            |     |

| 3.6.4 Subsystem Storage Protection                      | 3-5 | 5.4.4 Customer Engineer (CE)—SCD Mode                            |     |

| 3.6.5 Subspace Group Facility                           |     | 5.4.5 Access Administrator (AA)—MCD Mode                         |     |

| 3.7 Hardware System Area                                |     | ` '                                                              |     |

| 3.8 Integrated Disk                                     |     |                                                                  |     |

|                                                         |     | CHAPTER 6 SUPPORTED FEATURES AND FACILITIES                      |     |

| CHAPTER 4 CHANNEL SUBSYSTEM                             |     | 6.1 List of ESA/390 Features Dependent on Operation Mode         | 6-1 |

|                                                         |     | 6.2 List of Features Not Dependent on Mode                       |     |

| 4.1 Channel Subsystem Overview                          | 4-1 | 6.3 List of Features Contributing to RAS                         |     |

| 4.2 System Architecture Supported by Channel Subsystem  |     | 6.4 Feature Definitions                                          |     |

| 4.2.1 I/O Control Logic inside Instruction Processor    |     |                                                                  |     |

| 4.2.2 I/O Control Logic inside System Processor         |     |                                                                  |     |

| 4.2.3 Hardware System Area                              |     | CHAPTER 7 COOLANT DISTRIBUTION UNIT                              |     |

| 4.2.4 Unit Control Words and Logical Control Unit Words |     |                                                                  |     |

| 4.2.5 I/O Device Control by Channel Command Words       |     | 7.1 Overview                                                     | 7-1 |

| 4.3 Hardware Organization                               |     | 7.2 Function                                                     | 7-1 |

| 4.4 Channel Subsystem Functions                         |     |                                                                  |     |

| 4.5 Channel Subsystem Configuration                     |     |                                                                  |     |

| 4.5.1 Channel Subsystem Capacities                      |     |                                                                  |     |

| 4.5.2 CHPID Assignments                                 |     |                                                                  |     |

| CHAPTER 5 SERVICE PROCESSOR AND CONSOLE DEVICE          |     |                                                                  |     |

| 5.1 Overview of SVP/CD Subsystem                        |     |                                                                  |     |

| 5.2 SVP Hardware Design and Features                    | 5-2 |                                                                  |     |

| 5.2.1 SVP Hardware Design and Feature Summary           | 5-2 |                                                                  |     |

| 5.2.2 SVP Interface Design Notes                        |     |                                                                  |     |

| 5.2.3 SVP Logical Functions                             | 5-3 |                                                                  |     |

|                                                         |     |                                                                  |     |

# LIST OF FIGURES

# LIST OF TABLES

| 1-1 F-7C and F-7E Model Lineup                                 |     | 1-1 Determination of F-7C Base Models                                 | 1-2  |

|----------------------------------------------------------------|-----|-----------------------------------------------------------------------|------|

| 1-2 External View of F-7C Base and F-7C CF                     | 1-5 | 1-2 Determination of F-7C Turbo Models                                | 1-3  |

| 1-3 Processor Unit Frame Contents of F-7C Base and F-7C CF     | 1-5 | 1-3 Determination of F-7C CF Models                                   | 1-3  |

| 1-4 External View of F-7C Turbo and F-7E Turbo                 | 1-6 | 1-4 Determination of F-7E Turbo Models                                | 1-3  |

| 1-5 Processor Unit Frame Contents of F-7C Turbo and F-7E Turbo | 1-6 | 1-5 Numbers of Frames and Components by Processor Models              | 1-4  |

| 1-6 F-7C and F-7E Basic Logical Components                     |     | 1-6 Processor Configuration Summary of F-7C and F-7E Processor Models |      |

| 1-7 Configuration of F-7C 1SC Base Models and 2SC Base Models  | 1-7 | 1-7 F-7C and F-7E Processor Group Technology Summary                  | 1-11 |

| 1-8 Configuration of F-7C 2SC Turbo Models                     | 1-8 | 3-1 Cache Characteristics                                             |      |

| 1-9 Configuration of F-7C 1SC CF Models and 2SC CF Models      | 1-8 | 3-2 Available Processor Storage Sizes                                 | 3-4  |

| 1-10 Configuration of F-7E 2SC Turbo Models                    |     | 3-3 Calculation Models (Assumptions)                                  |      |

| 2-1 Examples of Virtual Address Formats                        |     | 3-4 Calculation Results (Typical HSA Sizes)                           |      |

| 3-1 Storage Hierarchy for F-7C and F-7E Models                 | 3-2 | 3-5 Limits for Integrated Disk and Its Associated Features            | 3-7  |

| 3-2 Processor Storage                                          | 3-3 | 4-1 Channel Subsystem Functions by Channel Type                       | 4-4  |

| 3-3 HSA in Basic Mode                                          | 3-6 | 4-2 Channel Subsystem Capacities                                      | 4-5  |

| 3-4 HSA in LPAR Mode with up to 2 GB MS                        |     | 4-3 Number of Channels Available                                      |      |

| 3-5 HSA in LPAR Mode with More than 2 GB up to 16 GB MS        | 3-6 | 4-4 CHPID Assignments on F-7C Base, F-7C Turbo, and F-7E Turbo        | 4-6  |

| 3-6 Processor Configuration with Integrated Disk               | 3-7 | 4-5 CHPID Assignments on F-7C CF                                      | 4-7  |

| 4-1 Hardware Organization of Each IOP                          | 4-4 | 5-1 CD Hardware Components                                            |      |

| 5-1 Console Subsystem Physical Positioning                     |     | 6-1 ESA/390 Features Dependent on Operation Mode                      |      |

| 5-2 SVP Hardware Design and Feature Summary                    |     | 6-2 Features Not Dependent on Mode                                    | 6-4  |

| 5-3 CD Physical Components                                     |     | 6-3 RAS Features                                                      |      |

| 7-1 Function of CDU in F-7C Turbo Models and F-7E Turbo Models | 7-1 |                                                                       |      |

| IST OF AB | BREVIATIONS                 |         |                            | EHSA  | Extended Hardware        | HDD         | hard disk drive             |

|-----------|-----------------------------|---------|----------------------------|-------|--------------------------|-------------|-----------------------------|

|           |                             |         |                            |       | System Area              | HDM         | High-Density Module         |

|           |                             |         |                            | EMIF  | ESCON Multiple           | HFC         | hydrofluorocarbon           |

| AA        | Access Administrator        | CH      | channel                    |       | Image Facility           | HMC         | Hardware Management         |

|           | (user level)                | CHP     | Channel Processor          | EN    | European Norm            |             | Console                     |

| ADMF      | Asynchronous Data Mover     | CHPID   | channel path ID            | ES    | expanded storage         | HSA         | Hardware System Area        |

|           | Facility                    | CH-PK   | channel package            | ESA   | Enterprise Systems       | IBM         | International Business      |

| AFT       | ASN first table             | CICS    | Customer Information       |       | Architecture             |             | <b>Machines Corporation</b> |

| AIX       | Advanced Interactive        |         | Control System             | ESCH  | Extended Serial          | <b>ICMF</b> | Integrated Coupling         |

|           | Executive                   | CM      | concurrent maintenance     |       | Channel                  |             | Migration Facility          |

| ALB       | ART Lookaside Buffer        | CMOS    | complementary metal        | ESCON | Enterprise Systems       | ID          | identifier                  |

| AO        | Advanced Operator (user     |         | oxide semiconductor        |       | Connection               | IDAW        | Indirect-Data-Address       |

|           | level)                      | CNC     | connection channel         | ETAF  | External Timer           |             | Word                        |

| AP        | Alternate Processor         | CP      | Central Processor; Control |       | Attachment Feature       | IDK         | Integrated Disk             |

| ART       | access register translation |         | Program                    | Ex-1  | Expansion Frame          | IEF         | Interpretive Execution      |

| ASN       | address-space number        | CPN     | Central Processor Node     | FAR   | floating address         |             | Facility                    |

| AST       | ASN second table            | CPU     | Central Processing Unit    |       | register                 | IML         | initial microcode loading   |

| ATM       | asynchronous transfer       | CTC     | channel-to-channel         | FBCH  | Fibre Channel            | IMS         | Information Management      |

|           | mode                        | CU      | control unit               | FCC   | Federal                  |             | System                      |

| BC-mode   | Basic Control mode          | CVC     | converter channel          |       | Communications           | IntCF       | Integrated Coupling         |

| BL        | block-multiplexer           | DASD    | direct access storage      |       | Commission               |             | Facility                    |

|           | (channel)                   |         | device                     | FCP   | Fibre Channel Protocol   | I/O         | input/output                |

| BPU       | Basic Processing Unit       | DAT     | dynamic address            | FDDI  | fiber distributed data   | IOCDS       | I/O Configuration Data      |

| BS        | buffer storage              |         | translation                |       | interface                |             | Set                         |

| BTA       | 1,2,3-Benzotriazole         | DB2     | Data Base 2                | FRR   | Functional Recovery      | IOCP        | I/O Configuration           |

| BY        | byte-multiplexer (channel)  | DCS     | dynamic channel            |       | Routine                  |             | Program                     |

| CCW       | channel command word        |         | subsystem                  | FRU   | field-replaceable unit   | IOP         | Input Output Processor      |

| CD        | Console Device              | DFSORT  | Data Facility Sort         | GB    | gigabyte(s)              | IP          | Instruction Processor       |

| CDU       | Coolant Distribution Unit   | DL/I    | Data Language I            | GUI   | graphical user interface | IPL         | initial program load        |

| CE        | Customer Engineer (user     | dpi     | dot per inch               | HCCF  | Highspeed Coupling       | ISCH        | Inter-System Coupling       |

|           | level)                      | DRM     | Dynamic I/O                |       | Control Feature          |             | Channel                     |

| CF        | coupling facility           |         | Reconfiguration            | HCCFA | Highspeed Coupling       | ISCH2       | Inter-System Coupling       |

| CFC       | chlorofluorocarbon          |         | Management                 |       | Control Feature Assist   |             | Channel 2                   |

| CFR       | coupling facility receiver  | DSP     | Disk System Processor      | HCD   | Hardware                 | KB          | kilobyte(s)                 |

|           | (channel)                   | DSR     | Dynamic Storage            |       | Configuration            | LAN         | local area network          |

| CFS       | coupling facility sender    |         | Reconfiguration            |       | Definition               | LAP         | low address protection      |

|           | (channel)                   | EC-mode | Extended Control mode      |       |                          | LCU         | logical control unit        |

|           |                             |         |                            |       |                          |             |                             |

| LCUW   | logical control unit word | PCU  | physical control unit         |

|--------|---------------------------|------|-------------------------------|

| LED    | light-emitting diode      | PE   | processor element             |

| LPAR   | Logically-Partitioned     | PER  | Program Event Recording       |

|        | (mode); logical partition | PK   | package                       |

| LRU    | least recently used       | PMC  | Processor Management          |

| LSI    | large-scale integration   |      | Console                       |

| MB     | megabyte(s)               | PMU  | Power Management Unit         |

| MCD    | Management Console        | ppm  | parts per million             |

|        | Device                    | PSA  | Prefixed Storage Area         |

| MHPGS  | Multiple High-            | PSTR | Processor Storage             |

|        | Performance Guest         | PSW  | program status word           |

|        | Support                   | RAM  | random access memory          |

| MLPF   | Multiple Logical          | RAS  | reliability, availability and |

|        | Processor Feature         |      | serviceability                |

| MO     | magneto-optical           | RCP  | real control program          |

| MS     | main storage              | RFU  | Refrigeration Unit            |

| MVPG   | Move Page (Facility 1)    | RMF  | Resource Measurement          |

| MVPG-2 | Move Page Facility 2      |      | Facility                      |

| MVS    | Multiple Virtual Storage  | RPC  | Remote PCI Controller         |

| NEMA   | National Electrical       | SACF | Set Address Space Control     |

|        | Manufacturers Association |      | Fast                          |

| OCF    | Open Systems Connection   | SAP  | System Assist Processor       |

|        | Feature                   | SC   | System Controller             |

| OEM    | original equipment        | SCD  | Service Console Device        |

|        | manufacturer; original    | SCP  | System Control Program        |

|        | equipment manufacturing   | SDC  | self-describing component     |

| Op     | Operator (user level)     | SIE  | start interpretive execution  |

| OS     | operating system(s)       | SP   | System Processor; System      |

| OSA    | Open Systems Adapter      |      | Programmer (user level)       |

| OSCH   | Open Systems Connection   | SPOC | single-point-of-control       |

|        | Channel                   | SSSP | Subsystem Storage             |

| OS/390 | Operating System/390      |      | Protection                    |

| PAF    | Processor Availability    | SVC  | Supervisor Call               |

|        | Facility                  | SVGA | Super Video Graphics          |

| PC     | personal computer         |      | Array                         |

| PCI    | power control interface   | SVP  | Service Processor             |

|        |                           |      |                               |

| SYSIML  | system initial             | UA   | unit address                 |

|---------|----------------------------|------|------------------------------|

|         | microprogram loading       | UCW  | unit control word            |

| Sysplex | System Complex             | VLSI | very large-scale integration |

| S/370   | System/370                 | VM   | Virtual Machine (operating   |

| S/390   | System/390                 |      | system)                      |

| TCP/IP  | Transmission Control       | VMA  | Virtual Machine Assist       |

|         | Protocol/Internet Protocol | VSE  | Virtual Storage Extended     |

| TIC     | transfer-in-channel        | VSF  | Virtual Server Facility      |

|         | (command)                  | WAN  | wide area network            |

| TLB     | Translation Lookaside      | WS   | work storage                 |

|         | Buffer                     | XA   | Extended Architecture        |

| TOD     | time-of-day                |      |                              |

| TSCF    | Target System Control      |      |                              |

|         | Facility                   |      |                              |

Note: Common abbreviations and instruction mnemonics are excluded.

#### CHAPTER 1 F-7C AND F-7E PROCESSOR GROUP OVERVIEW

# 1.1 Introduction

The F-7C and F-7E Processor Group is a group of processors based on complementary metal oxide semiconductor (CMOS) technology featured with cost-efficient capacity, flexibility, and processing power in a small footprint. The F-7C and F-7E Processor Group consists of the F-7C Base Models, the F-7C Turbo Models (performance-boosted models of F-7C), the F-7C CF Models (coupling facility models), and the F-7E Turbo Models (performance-boosted models beyond F-7C). The F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models support ESA/390 and S/390 industry standards and an extensive range of system software scenarios. All these models function in nonparallel or Parallel Sysplex environments, operating in either Basic or LPAR (logically-partitioned) mode. Each F-7C Base Model, each F-7C Turbo Model, and each F-7E Turbo Model also support various types of industry-standard channels— ESCON, parallel, coupling link, and OCF— in separate, intermixed, or shared configurations. By contrast, the F-7C CF Models act as coupling facilities in Parallel Sysplex environments, operating in LPAR mode. Each F-7C CF Model utilizes the same hardware technologies as the F-7C Base Models, and supports coupling link channels in separate, intermixed, or shared configurations.

The F-7C and F-7E processor lines are progressively scaled so that each succeeding processor model provides greater processing power while retaining many configuration possibilities. This scalability assures that upgrades can be easily sized for a particular situation and designed for minimal disruption.

# 1.2 Model Grouping

Depending on the purpose and the hardware implementation represented by the number of System Controllers (SCs), the F-7C Processor Group provides 1SC Base Models, 2SC Base Models, 1SC CF Models, and 2SC CF Models.

The F-7E Processor Group further extends the said scalability with performance-boosted 2SC Turbo Models.

Each F-7C Base Model uses a three- or four-character model ID, where the first character shows the number of [regular] Instruction Processors (IPs), the second character shows the number of SCs, the third character identifies the processor series "C" (fixed), and the fourth character indicates degraded or full performance: D degraded, blank full. Similarly, each F-7C Turbo Model and each F-7E Turbo Model use three- or four-character model ID, where the first character shows the number of [regular] IPs, the second character "2" (fixed) shows the number of SCs, the third character "C" or "E" identifies the processor series, and, where applicable, the fourth character "H" (fixed) indicates the processor module hardware type of boosted performance. For the F-7C CF Models, "0XC" is fixed to identify the CF Model, followed by three characters in parenthesis: the first character shows the number of Integrated Coupling Facility (IntCF) IPs, the second character shows the number of SCs, and the third character identifies the processor series "C" (fixed).

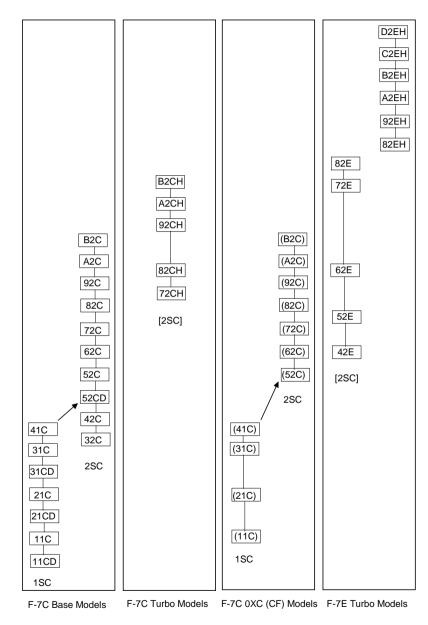

Figure 1-1 shows the F-7C and F-7E model lineup. Tables 1-1 through 1-4 show determination of specific processor models in the F-7C and F-7E lines.

Figure 1-1 F-7C and F-7E Model Lineup

Table 1-1 Determination of F-7C Base Models

| Model | l    | No. of        | No. of |       | No.       | of APs |                  | 9672, R6  |

|-------|------|---------------|--------|-------|-----------|--------|------------------|-----------|

|       |      | [Regular] IPs | SCs    | Total | IntCF IPs | DSPs   | Standby APs      | Ver. Code |

| 1SC   | 11CD | 1             | 1      | 1     | 0–1       | 0–1    | Δ                | 8F        |

| Base  |      |               |        | 4*    | 0–4*      | 0–2*   | $\Delta^*$       | 8F        |

|       | 11C  | 1             | 1      | 1     | 0–1       | 0–1    | Δ                | 81        |

|       |      |               |        | 4*    | 0–4*      | 0–2*   | $\Delta^*$       | 81        |

|       | 21CD | 2             | 1      | 3     | 0–3       | 0–2    | Δ                | 8E        |

|       | 21C  | 2             | 1      | 3     | 0–3       | 0–2    | Δ                | 82        |

|       | 31CD | 3             | 1      | 2     | 0–2       | 0–2    | Δ                | 03        |

|       | 31C  | 3             | 1      | 2     | 0–2       | 0–2    | Δ                | 8D        |

|       | 41C  | 4             | 1      | 1     | 0–1       | 0–1    | Δ                | 8C        |

| 2SC   | 32C  | 3             | 2      | 2     | 0–2       | 0–2    | Δ                | 83        |

| Base  |      |               |        | 5*    | 0–5*      | 0–2*   | $\Delta^{ullet}$ | 83        |

|       |      |               |        | 8*    | 0–8*      | 0–2*   | $\Delta^{ullet}$ | 83        |

|       | 42C  | 4             | 2      | 1     | 0–1       | 0–1    | Δ                | 84        |

|       |      |               |        | 4*    | 0–4*      | 0–2*   | $\Delta^{ullet}$ | 84        |

|       |      |               |        | 7*    | 0–7*      | 0–2*   | $\Delta^{ullet}$ | 84        |

|       | 52CD | 5             | 2      | 3     | 0–3       | 0–2    | $\Delta$         | 05        |

|       |      |               |        | 6*    | 0–6*      | 0–2*   | $\Delta^{\star}$ | 05        |

|       | 52C  | 5             | 2      | 3     | 0–3       | 0–2    | $\Delta$         | 85        |

|       |      |               |        | 6*    | 0–6*      | 0–2*   | $\Delta^{ullet}$ | 85        |

|       | 62C  | 6             | 2      | 2     | 0–2       | 0–2    | $\Delta$         | 86        |

|       |      |               |        | 5*    | 0–5*      | 0–2*   | $\Delta^{ullet}$ | 86        |

|       | 72C  | 7             | 2      | 1     | 0–1       | 0–1    | $\Delta$         | 87        |

|       |      |               |        | 4*    | 0–4*      | 0–2*   | $\Delta^{ullet}$ | 87        |

|       | 82C  | 8             | 2      | 3     | 0–3       | 0–2    | Δ                | 88        |

|       | 92C  | 9             | 2      | 2     | 0–2       | 0–2    | Δ                | 89        |

|       | A2C  | 10            | 2      | 1     | 0–1       | 0–1    | Δ                | A8        |

|       | B2C  | 11            | 2      | 0     | 0         | NA     | 0                | 0B        |

Δ Total minus IntCF IPs and DSPs. \* Optional configuration.

Table 1-2 Determination of F-7C Turbo Models

| Model |      | No. of        | No. of |       | No. of APs                  |   |           |

|-------|------|---------------|--------|-------|-----------------------------|---|-----------|

|       |      | [Regular] IPs | SCs    | Total | Total IntCF IPs Standby APs |   | Ver. Code |

| [2SC] | 72CH | 7             | 2      | 4     | 0–4                         | Δ | 4D        |

| Turbo | 82CH | 8             | 2      | 3     | 0–3                         | Δ | 4C        |

|       | 92CH | 9             | 2      | 2     | 0–2                         | Δ | 4B        |

|       | A2CH | 10            | 2      | 1     | 0–1                         | Δ | 8B        |

|       | B2CH | 11            | 2      | 0     | 0                           | 0 | 0F        |

Δ Total minus IntCF IPs.

Table 1-3 Determination of F-7C CF Models

| Mode      | I         | No. of        | No. of |       | No. of A  | Ps          | 9672, R6  |

|-----------|-----------|---------------|--------|-------|-----------|-------------|-----------|

|           |           | [Regular] IPs | SCs    | Total | IntCF IPs | Standby APs | Ver. Code |

| 1SC       | 0XC (11C) | 0             | 1      | 2     | 1         | 1           | 80        |

| CF        | 0XC (21C) | 0             | 1      | 5     | 2         | 3           | 80        |

|           | 0XC (31C) | 0             | 1      | 5     | 3         | 2           | 80        |

|           | 0XC (41C) | 0             | 1      | 5     | 4         | 1           | 80        |

| 2SC<br>CF | 0XC (52C) | 0             | 2      | 8     | 5         | 3           | 80        |

| CF        | 0XC (62C) | 0             | 2      | 8     | 6         | 2           | 80        |

|           | 0XC (72C) | 0             | 2      | 8     | 7         | 1           | 80        |

|           | 0XC (82C) | 0             | 2      | 11    | 8         | 3           | 80        |

|           | 0XC (92C) | 0             | 2      | 11    | 9         | 2           | 80        |

|           | 0XC (A2C) | 0             | 2      | 11    | 10        | 1           | 80        |

|           | 0XC (B2C) | 0             | 2      | 11    | 11        | 0           | 80        |

Table 1-4 Determination of F-7E Turbo Models

| Model |      | No. of        | No. of |       | No.       | of APs |             | 9672, R6  |

|-------|------|---------------|--------|-------|-----------|--------|-------------|-----------|

|       |      | [Regular] IPs | SCs    | Total | IntCF IPs | DSPs   | Standby APs | Ver. Code |

| [2SC] | 42E  | 4             | 2      | 2     | 0–2       | 0–2    | Δ           | TBD       |

| Turbo | 52E  | 5             | 2      | 1     | 0–1       | 0–1    | Δ           | TBD       |

|       | 62E  | 6             | 2      | 3     | 0–3       | 0–2    | Δ           | TBD       |

|       | 72E  | 7             | 2      | 2     | 0–2       | 0–2    | Δ           | TBD       |

|       | 82E  | 8             | 2      | 1     | 0–1       | NA     | Δ           | TBD       |

|       | 82EH | 8             | 2      | 3     | 0–3       | 0–2    | Δ           | TBD       |

|       | 92EH | 9             | 2      | 2     | 0–2       | 0–2    | Δ           | TBD       |

|       | A2EH | 10            | 2      | 1     | 0–1       | 0–1    | Δ           | TBD       |

|       | B2EH | 11            | 2      | 2     | 0–2       | 0–2    | Δ           | TBD       |

|       | C2EH | 12            | 2      | 1     | 0–1       | 0–1    | Δ           | TBD       |

|       | D2EH | 13            | 2      | 0     | 0         | NA     | 0           | TBD       |

Δ Total minus IntCF IPs and DSPs.

#### 1.3 Benefits

The F-7C and F-7E Processor Group provides an extensive range of functionality and processing scale. The general benefits are explained in the following subsections.

# 1.3.1 Leading-Edge Technologies

The F-7C and F-7E processor models utilize high-density modules, advanced logic design based on CMOS, and other technologies to enhance the overall performance.

# 1.3.2 Excellent Performance Efficiencies

The use of CMOS with other enhancing technologies, streamlined component design, and advanced diagnostics provide the following performance benefits:

- Lower operating costs

- Greatly-reduced footprints

- Noticeably improved resource usage

- Enhanced reliability, availability, and serviceability (RAS)

- Improved results in better price-to-performance ratios

# 1.3.3 Full Compatibility

All the F-7C Base Models, F-7C Turbo Models, and F-7E Turbo Models support full S/390 industry standards and ESA/390 architecture in parallel and non-parallel environments. All the F-7C CF Models support S/390-compatible coupling facility (CF) functions in parallel environments. Multiple Logical Processor Feature supports up to 15 LPARs on all models of the F-7C and F-7E Processor Group. Each LPAR in turn supports ESA/390 architecture or S/390-compatible CF functions on all the F-7C Base Models, F-7C Turbo Models, and F-7E Turbo Models, and S/390-compatible CF functions on all the F-7C CF Models.

# 1.3.4 Balanced Scalability

Scaling provides the ability to create subtle and not-so-subtle configuration and performance differences within the same model. When extended among the wide range of the F-7C and F-7E lines, scaling simplifies upgrading from one model to another. In both instances, scaling provides configuration flexibility and compatibility which simplifies meeting changing business requirements.

#### 1.3.5 Optimized Reliability, Availability, and Serviceability

The F-7C and F-7E processor models use minimal physical components and connection points to simplify the design and reduce the chance of error. The use of CMOS chips and high-density semiconductor packaging creates a tough superstructure that withstands excessive physical stress and helps minimize disruption due to physical damage.

Additionally, the F-7C and F-7E processor models are backed by comprehensive professional services and technical support which includes online diagnostics and other nondisruptive maintenance techniques.

# 1.4 Physical Design Highlights

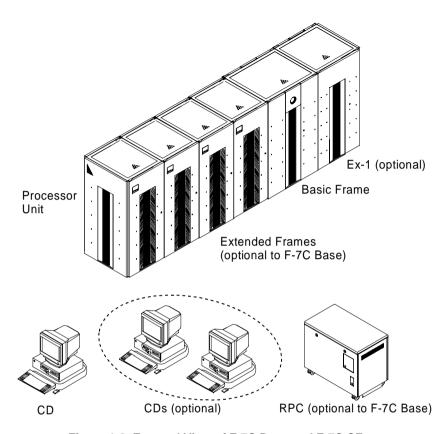

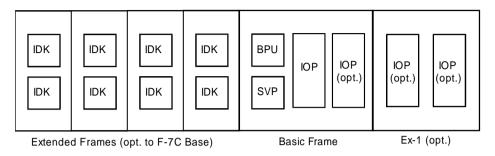

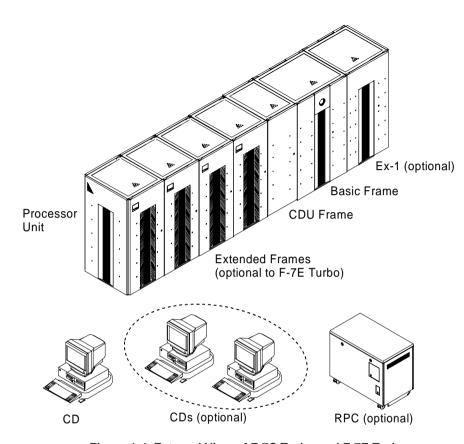

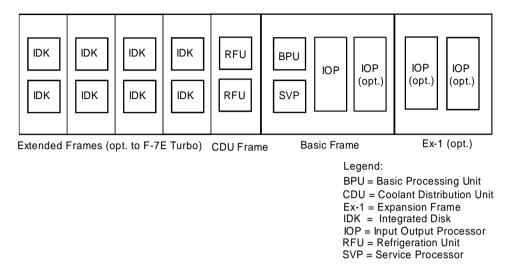

The F-7C and F-7E processor models each integrate the Basic Processing Unit (BPU), the Service Processor (SVP), power supplies, and one standard Input Output Processor (IOP) and one optional IOP into a single cabinet called Basic Frame. The BPU contains all the hardware for the Instruction Processor (IP), System Processor (SP), Processor Storage (PSTR), and System Controller (SC).

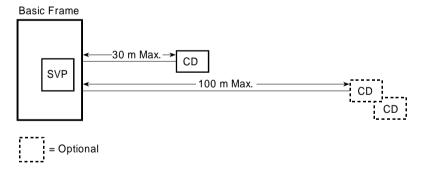

One Expansion Frame (Ex-1) may be needed to house up to two more units of optional IOP. The necessity of the Ex-1 depends upon the number of channels to be installed and their channel path IDs to be assigned. The Ex-1 incorporates cooling fans and power supplies.

Up to four Extended Frames are optionally installable for support of the Integrated Disk (IDK) on the F-7C Base Models except B2C models and on the F-7E Turbo Models except 82E and D2EH models. One Extended Frame accommodates two IDKs.

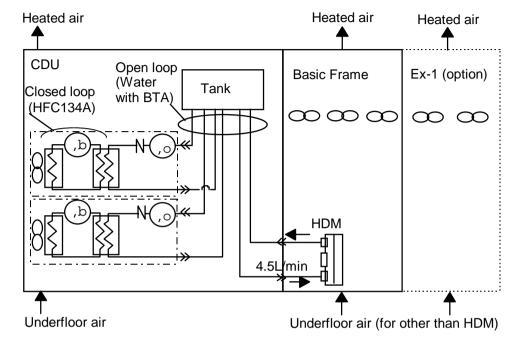

One Coolant Distribution Unit (CDU) Frame is mandatory on each F-7C Turbo Model and F-7E Turbo Model to achieve its performance boost through reinforced cooling of processor elements. The CDU Frame incorporates power supplies and dualized Refrigeration Units (RFUs).

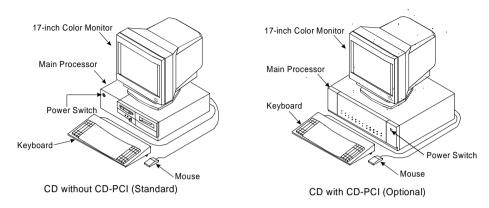

One through three Console Devices (CDs) and up to four optional Remote PCI Controllers (RPCs) are each housed in separate cabinets.

Table 1-5 shows the number of frames and components of the F-7C and F-7E processor models. Figures 1-2 through 1-5 illustrate the external views and frame contents of the F-7C processor models.

Table 1-5 Numbers of Frames and Components by Processor Models

| Fram  | e or Component      |      | (    | Q'ty on F-7 | 7C     |        | Q'ty on F-7E |

|-------|---------------------|------|------|-------------|--------|--------|--------------|

|       |                     | 1SC  | 2SC  | [2SC]       | 1SC CF | 2SC CF | [2SC] Turbo  |

|       |                     | Base | Base | Turbo       |        |        |              |

| Basic | Frame               | 1    | 1    | 1           | 1      | 1      | 1            |

|       | BPU                 | 1    | 1    | 1           | 1      | 1      | 1            |

|       | IOP                 | 1–2  | 1–2  | 1–2         | 1–2    | 1–2    | 1–2          |

|       | SVP                 | 1    | 1    | 1           | 1      | 1      | 1            |

| Ex-1  | (option)            | 0–1  | 0–1  | 0–1         | 0–1    | 0–1    | 0–1          |

|       | IOP (option)        | 0–2  | 0–2  | 0–2         | 0–2    | 0–2    | 0–2          |

| Exter | nded Frame (option) | 0–4  | 0–4  | NA          | NA     | NA     | 0–4          |

|       | IDK (option)        | 0–8  | 0–8  | NA          | NA     | NA     | 8–0          |

| CDU   | Frame               | NA   | NA   | 1           | NA     | NA     | 1            |

| CD    |                     | 1–3  | 1–3  | 1–3         | 1–3    | 1–3    | 1–3          |

| RPC   | (option)            | 0–4  | 0–4  | 0–4         | NA     | NA     | 0–4          |

Figure 1-2 External View of F-7C Base and F-7C CF

Legend:

BPU = Basic Processing Unit

Ex-1 = Expansion Frame

IDK = Integrated Disk

IOP = Input Output Processor SVP = Service Processor

Figure 1-3 Processor Unit Frame Contents of F-7C Base and F-7C CF

Figure 1-4 External View of F-7C Turbo and F-7E Turbo

Figure 1-5 Processor Unit Frame Contents of F-7C Turbo and F-7E Turbo

# 1.5 Configuration

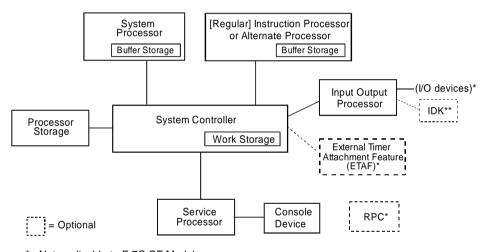

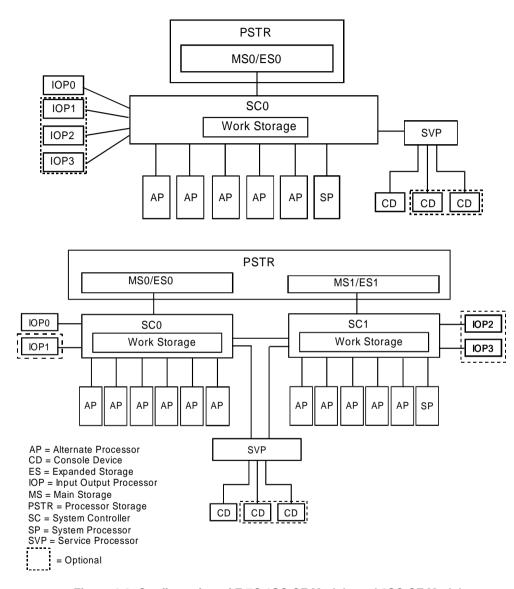

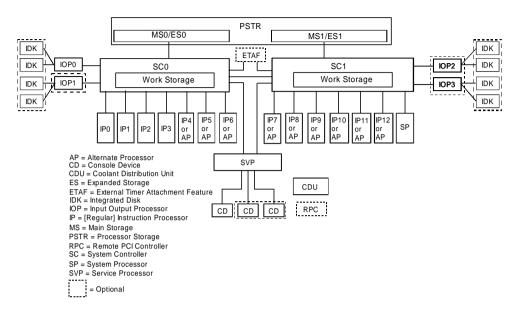

Figure 1-6 conceptually illustrates how the basic elements of the F-7C and F-7E processor models are configured in relationship with each other. Note that each box does not represent a single distinct physical component, but rather a logical component that performs a general function using an aggregate of physical components.

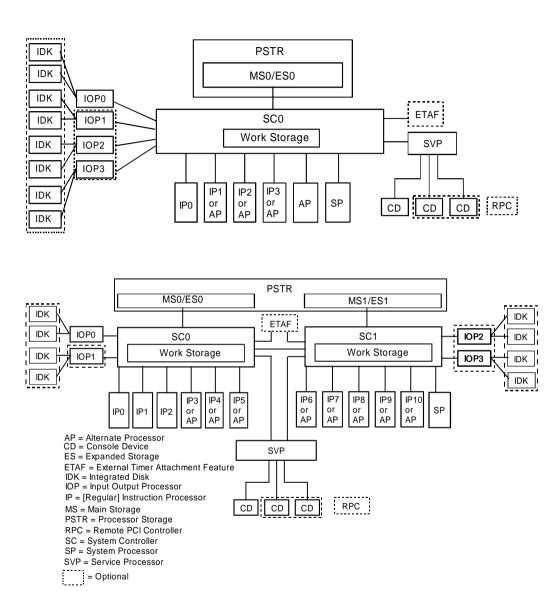

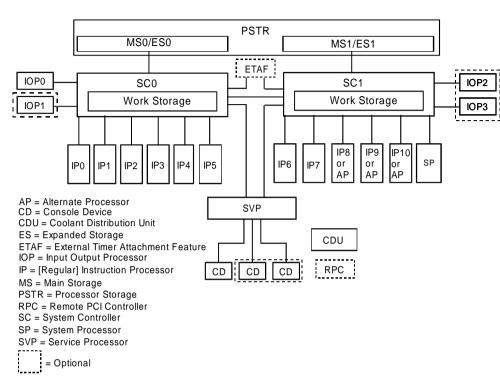

Figures 1-7 through 1-10 illustrate possible configurations for the F-7C and F-7E processor models. Following these figures are subsections 1.5.1 through 1.5.6 that provide description of each component and summary of the processor configurations.

- \* Not applicable to F-7C CF Models.

- \*\* Only applicable to F-7C Base Models other than B2C and F-7E Turbo Models other than 82E and D2EH.

Figure 1-6 F-7C and F-7E Basic Logical Components

Figure 1-7 Configuration of F-7C 1SC Base Models and 2SC Base Models

Figure 1-8 Configuration of F-7C 2SC Turbo Models

Figure 1-9 Configuration of F-7C 1SC CF Models and 2SC CF Models

Figure 1-10 Configuration of F-7E 2SC Turbo Models

#### 1.5.1 Instruction Processor and System Processor

The Instruction Processors (IPs) and System Processor (SP) manage the execution of program instructions and the architectural facilities for their support. The F-7C Base Models, F-7C Turbo Models, and F-7E Turbo Models support all instruction formats and instructions defined in IBM's *Enterprise Systems Architecture/390 Principles of Operation*.

Each processor is an aggregate of physically-associated processing circuitry and cache memory arrays. Each F-7C and F-7E processor model has all of its processors and associated cache in a single High-Density Module (HDM).

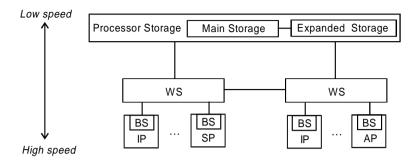

Two levels of cache (high speed buffer storage) reside between the IPs (and SP) and the main storage: Buffer Storage (BS) and Work Storage (WS). Cache improves processor performance by reducing the effects of delays encountered when a process fetches data from main storage.

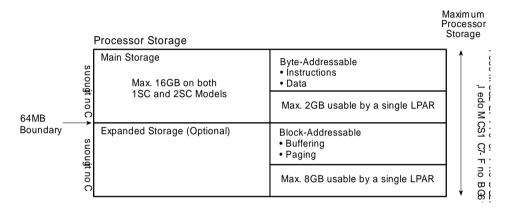

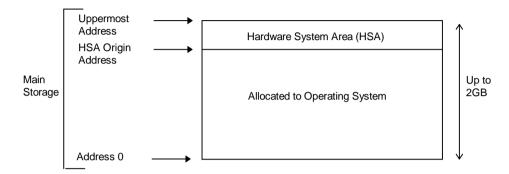

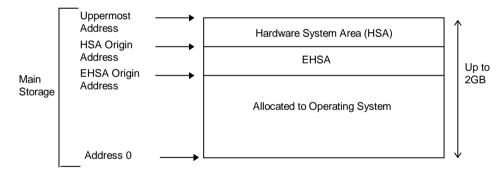

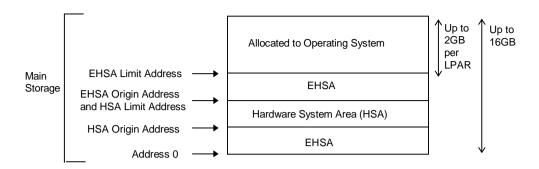

# 1.5.2 System Controller and Processor Storage

The System Controller (SC) manages access to all of the processor's physical storage called processor storage. Processor storage provides all the storage capacity for each processor complex. The F-7C and F-7E models partition processor storage into main storage and optional expanded storage.

The basic addressable storage unit in main storage is the 8-bit byte. This byte can be used as a single hexadecimal character, as 2 decimal digits, or as 8 binary digits. All architecturally-defined data formats are supported.

On the F-7C 1SC Base Models and F-7C 1SC CF Models, the maximum amount of installable processor storage is 16 GB. On the F-7C 2SC Base Models, F-7C Turbo Models, F-7C 2SC CF Models, and F-7E Turbo Models, the maximum amount of installable processor storage is 32 GB.

In Basic (non-LPAR) mode running under ESA/390, main storage is limited to 2 GB with all the remaining processor storage assignable to expanded storage.

In LPAR mode running under Multiple Logical Processor Feature, the F-7C and F-7E models (both 1SC and 2SC) can partition up to 16 GB of processor storage as main storage to be sub-allocated to LPARs. Then, each LPAR is limited to 2 GB of main storage.

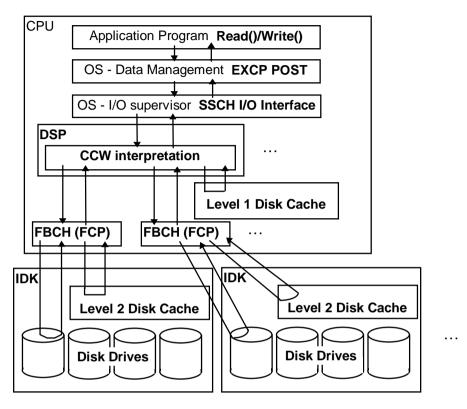

# 1.5.3 Input/Output Device Management

The Input Output Processor (IOP) manages channels to which are attached all I/O devices except the Console Device (CD). The Service Processor (SVP) manages all CDs.

The channel subsystem contains IOPs, the channels they support, and the IOP-associated logic residing in the IPs. This subsystem manages all I/O activity independent of the IPs to allow the channels and processors to work simultaneously with minimal wait for I/O operations to complete.

The channel subsystem supports the following combinations of channels depending on the processor models:

- F-7C Base: ESCH (ESCON), parallel, ISCH2 (coupling link), Open Systems Connection Feature (OCF) channels, and Fibre Channel (FBCH) of Fibre Channel Protocol (FCP) channel type\*

- F-7C Turbo: ESCH (ESCON), parallel, ISCH2 (coupling link), and Open Systems Connection Feature (OCF) channels

- F-7C CF: ISCH2 channels

- F-7E Turbo: ESCH (ESCON), parallel, ISCH2 (coupling link), Open Systems Connection Feature (OCF) channels, and Fibre Channel (FBCH) of Fibre Channel Protocol (FCP) channel type\*

- \* Dedicated to Integrated Disk (IDK).

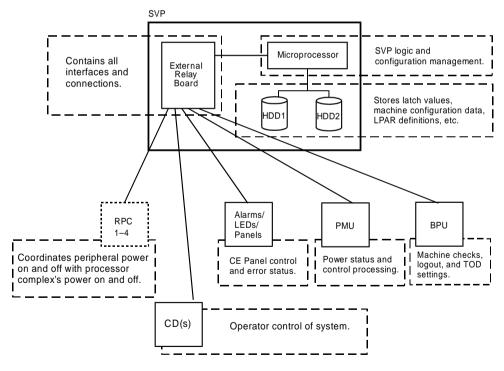

## 1.5.4 SVP/CD Subsystem

The SVP/CD subsystem contains the Service Processor (SVP) which supports one to three CDs and the optional interfaces to the Processor Management Console (PMC) and Hardware Management Console (HMC). These consoles can also back up a regular operator console when needed.

# 1.5.5 Optional Components

The following are optional, where "\*" indicates "NA on F-7C CF Models" and "\*\*" indicates "only applicable to F-7C Base Models and F-7E Turbo Models":

- Processor storage

- Channels: ESCON-compatible ESCH (multimode duplex)\*, Parallel\*, OCF\*, FBCH (FCP)\*\*, and ISCH2 coupling link (single-mode duplex)

- Remote PCI Controller\*

- Additional Console Devices

- External Timer Attachment Feature (ETAF)\*

- Integrated Disk (IDK)\*\*

# 1.5.6 Processor Configuration Summary

Table 1-6 provides processor configuration summary of the F-7C and F-7E processor models.

Table 1-6 Processor Configuration Summary of F-7C and F-7E Processor Models

| Component |       |             | Q'ty on F-7C |        |        |        |             | Q'ty on F-7E |

|-----------|-------|-------------|--------------|--------|--------|--------|-------------|--------------|

|           |       | 1SC         | 2SC          | [2SC]  | 1SC CF | 2SC CF | [2SC] Turbo |              |

|           |       |             | Base         | Base   | Turbo  |        |             |              |

| Processor | [Re   | gular] IP   | 1–4          | 3–11   | 7–11   | 0      | 0           | 4–13         |

| elements  | SP    |             | 1            | 1      | 1      | 1      | 1           | 1            |

|           | SC    |             | 1            | 2      | 2      | 1      | 2           | 2            |

|           | ΑP    | Total       | 1–4          | 0–8    | 0–4    | 2–5    | 8–11        | 0–3          |

|           |       | IntCF IP    | 0–3          | 0–3    | 0–4    | 1–4    | 5–11        | 0–3          |

|           |       |             | (0-4*)       | (0-8*) |        |        |             |              |

|           |       | DSP         | 0–2          | 0–2    | -      | _      | _           | 0–2          |

|           |       | Standby AP  | Δ            | Δ      | Δ      | Δ      | Δ           | Δ            |

| Max. PSTF | ₹ ca  | pacity (GB) | 16           | 32     | 32     | 16     | 32          | 32           |

| ETAF      |       |             | 0–1          | 0–1    | 0–1    | _      | -           | 0–1          |

| IOP       |       |             | 1–4          | 1–4    | 1–4    | 1–4    | 1–4         | 1–4          |

| Channel   | Par   | allel       | 0–96         | 0–96   | 0–96   | _      | _           | 0–96         |

|           | ES    | CH          | 0-256        | 0-256  | 0-256  | _      | _           | 0-256        |

|           | ISC   | H2          | 0-32         | 0-32   | 0-32   | 0-32   | 0-32        | 0–32         |

|           | OC    | F           | 0–12         | 0–12   | 0–12   | _      | _           | 0–12         |

|           | FB    | CH (FCP)    | 0–16         | 0–16   | -      | _      | _           | 0–16         |

|           | Total |             | 8-256        | 8-256  | 8-256  | 2-32   | 2–32        | 8-256        |

| CDU       |       | _           | -            | 1      | _      | _      | 1           |              |

| SVP and   | SV    | Ρ           | 1            | 1      | 1      | 1      | 1           | 1            |

| CD        | CD    |             | 1–3          | 1–3    | 1–3    | 1–3    | 1–3         | 1–3          |

| RPC       |       | 0–4         | 0–4          | 0–4    | _      | _      | 0–4         |              |

<sup>\*</sup> Optional configuration.  $\Delta$  Total minus IntCF IPs and DSPs.

# 1.6 System Design Highlights

# 1.6.1 Operating System Support

The following are supported by the F-7C Base Models, F-7C Turbo Models, and F-7E Turbo Models:

- OS/390

- MVS/ESA 4.3, 5.1, 5.2 and subsequent releases

- VM/ESA 1.2.2, 2.1, 2.2, 2.3

- VSE/ESA 1.4, 2.1, 2.2, 2.3

# 1.6.2 Advanced Logic Design

The F-7C and F-7E processor models enhance overall performance using a design that optimizes combined and individual aspects when integrating components. Techniques and technologies used include:

- · High-speed system cycles and execution

- High-speed/high-density IOPs and channels built on CMOS LSI

- Execution pipeline controls

- Multilevel storage hierarchy

#### 1.6.3 CPU ID

The F-7C and F-7E processor models generate CPU ID information which is presented to software through the use of STORE CPU ID (STIDP) instruction. The 8-byte data area returned by STIDP contains a version code which identifies the processor model, a CPU identification number which is unique to each IP, a model number (which identifies the entire F-7C and F-7E processor models as "9672"), and 2 bytes of hexadecimal zero padding on the right. STIDP returns this data in the following format:

The format of the CPU Identification Number field is different when the system runs in Basic mode and when it runs in LPAR mode.

In Basic mode, the CPU Identification Number identifies the physical IP by the following format:

In LPAR mode, the CPU Identification Number identifies the logical IP by the following format:

Each field of the CPU ID information contains the following:

- Version Code: Two hexadecimal digits identifying the processor model. See section 1.2, tables 1-1 through 1-4.

- CPU Identification Number

- I: Physical CPU address as 1 hexadecimal digit.

- L: Logical CPU address as 1 hexadecimal digit.

- P: LPAR number as 1 hexadecimal digit.

- SSSSS or SSSS: Serial number as 5 or 4 hexadecimal digits derived from the low order digits of the system serial number.

- Model Number: "9672" as 4 hexadecimal digits.

- 0000: "0000" as 4 hexadecimal digits.

## 1.6.4 Packaging Technology

The F-7C and F-7E processor components use the design features for optimum packaging and performance. Table 1-7 summarizes the characteristics of the primary technologies used by the F-7C and F-7E processor models. Following this table are explanations about such technologies and how they affect functionality.

Table 1-7 F-7C and F-7E Processor Group Technology Summary

| Component         | Topic              | Characteristics                           |

|-------------------|--------------------|-------------------------------------------|

| Logic LSIs in     | Technology         | CMOS                                      |

| IPs and SP        | No. of transistors | 25 million                                |

| Memory LSIs in    | Technology         | CMOS                                      |

| Processor Storage | Capacity per chip  | 64, 128, or 256 Mbits                     |

| Logic LSIs in IOP | Technology         | CMOS                                      |

| High-Density      | Material           | Glass ceramic                             |

| Module (HDM)      | Size (mm)          | 136 × 136                                 |

|                   | No. of layers      | 55                                        |

|                   | No. of pins        | 5042                                      |

|                   | No. of LSIs (Max.) | 36                                        |

|                   | No. of IPs (Max.)  | 11 on F-7C, 13 on F-7E                    |

| Processor Package | Size (mm)          | 364 × 534                                 |

|                   | No. of layers      | 30                                        |

|                   | No. of HDMs        | 1                                         |

| Cooling           | Method             | F-7C Base or F-7C CF: air                 |

|                   |                    | • F-7C Turbo or F-7E Turbo: air and water |

# Chip technologies

Explained below are chip technologies used in the F-7C and F-7E processor models.

- Logic LSIs in IPs and SP: The Instruction Processors (IPs) and System Processor (SP) use high-speed, high-density, CMOS-based LSIs. CMOS technology increases the number of logic gates per chip and reduces the distance that signals must travel between gates. This high gate density (25 million transistors per chip) enables functions previously using multiple chips to be consolidated onto a single chip. Similarly, functions previously requiring multiple cards or modules are consolidated into a single multi-chip package.

- Memory LSIs in Processor Storage: Processor Storage uses 64, 128, or 256 M-bit CMOS-based memory LSIs. These chips sustain high memory throughput and reduce the physical frame size and footprint used by large-capacity processor storage.

- Logic LSIs in IOPs: The Input Output Processors (IOPs) use logic-in-RAM CMOS LSIs. Each is made up of a 364-kilobit RAM and a 1,150-kilogate logic area. This technology, in conjunction with circuitry innovations, allows concurrent channel maintenance and packaging efficiencies.

# High-Density Module (HDM)

On each system, a single High-Density Module (HDM) comprises Instruction Processors (IPs), System Processor (SP), cache, and System Controller (SC). The HDM is a very small package providing excellent environmental characteristics.

# Processor Package

Processor Package comprises HDM, Processor Storages, and Key Storages.

# Cooling

The F-7C Base Models and CF Models use air-cooling technology only. The F-7C Turbo Models and F-7E Turbo Models use water for cooling on the HDM and air for cooling on the other components. For cooling specifications, see *F-7C and F-7E Processor Group Installation Planning Guide* (F7-GA-1C02).

# 1.7 Functional Design Highlights

The following lists the main facilities and features supported by the design of the F-7C and F-7E processor models, where "\*" indicates "Not available or not effective on F-7C CF Models." For further information, refer to the subsections that follow.

- ESA/390 architecture support\*

- S/390 architectural features and functions\*

- SIE compatibility\*

- Parallel Sysplex computing

- LPAR support

- Virtual Server Facility Phase-1\*

- ESCON Channel compatibility\*

- Parallel channel support\*

- Open Systems Connection Feature (OCF)\*

- Console support including GUI and security

- Reliability, Availability, and Serviceability approach to non-stop computing

#### 1.7.1 ESA/390 Architecture Support

The F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models support ESA/390 architecture operationally in Basic mode, in LPAR mode, or as a guest virtual machine.

The F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models provide the necessary hardware characteristics to fully support ESA/390 architecture, including:

- Large storage capacity

- High speed data transfer using:

- Parallel channels

- Extended Serial Channels (ESCHs)

- Inter-System Coupling Channels 2 (ISCH2s)

#### 1.7.2 S/390 Architectural Features and Functions

The F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models provide complete compatibility for all S/390 features and functions. The following is a partial list of features supported. Refer to chapter 6 for further details and for a complete listing of which features are supported in ESA/390 mode.

- Asynchronous Data Mover Facility (ADMF)

- Asynchronous Page-out Facility

- Called Space Identifiers

- Cancel I/O

- Checksum

- Compare-and-Move Extend

- Data Compression

- Dynamic I/O Reconfiguration Management (DRM)

- Enhanced Move-Page (MVPG-2)

- Immediate-and-Relative Instructions

- Logical String Assist

- Parallel Sysplex participation

- Scalar Square Root Instructions

- Set Address Space Control Fast (SACF)

- Subspace Group Facility

- Subsystem Storage Protection (SSSP)

- Suppression on Protection

# 1.7.3 SIE Compatibility

All characteristics and functions needed to support SIE compatibility are provided on the F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models including:

- Expedited SIE

- Interpreted SIE

- Multiple High Performance Guest Support (MHPGS)

- Region Relocation Facility for VM

- Region Relocation Facility for MLPF

# 1.7.4 Parallel Sysplex Computing

The F-7C and F-7E processor models fully participate in a Parallel Sysplex environment, or implement Parallel Sysplex by providing connectivity to a coupling facility function.

As a participant in a Parallel Sysplex environment, the F-7C and F-7E processor models provide:

- Coupling code called Highspeed Coupling Control Feature Assist (HCCFA) effective under MLPF

- Connectivity to coupling facility via Inter-System Coupling Channels 2 (ISCH2s)

- Connectivity to the Sysplex Timer via External Timer Attachment Feature (ETAF)

- ESCH channels

- Support for MVS/ESA, Ver. 5 and OS/390

To implements a Parallel Sysplex environment, the F-7C and F-7E processor models provide:

- ISCH environment with standalone HCCF or F-7C CF Model

- ISCH environment with logically-partitioned HCCF

- ICMF environment

# 1.7.5 LPAR Support

Multiple Logical Processor Feature (MLPF) supports up to 15 logical partitions (LPARs) which enables the use of a logically-partitioned operating mode. Other support for LPARs includes:

- Dynamic storage reconfiguration

- ESA/390 architecture support (F-7C Base Models, F-7C Turbo Models, and F-7E Turbo Models only)

- Support for up to a 16 GB pool of main storage for LPARs (a single LPAR cannot exceed 2 GB)

# 1.7.6 Virtual Server Facility Phase-1

Virtual Server Facility (VSF) Phase-1 provides the user with virtually fenced, fixed groups of physical IPs called "Virtual Servers" under MLPF on the F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models. Each virtual server has a unique set of version code and serial number to be reasonably determined by the capacity of the server, thus contributing to possible reduction of the user's software cost. Changes to the physical IP grouping are only allowed to the OEM customer's authorized service representative.

# 1.7.7 ESCON Channel Compatibility

The F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models provide the ESCH channels compatible with IBM's ESCON:

- ESCON architecture and protocols

- Fiber optic cabling capability

- Dynamic connectivity

- Connectivity to ESCON Directors

- Connectivity to ESCON Converters (9034, Model 1 and Model 2)

- 17 MB/s data rate

- Connectivity to multimode fiber optic cable

- ESCON Multiple Image Facility (EMIF)

# 1.7.8 Parallel Channel Support

Parallel channels are fully supported on the F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models to allow attachment of pre-ESCON devices via bus and tag cables. Parallel channels support data rates up to 4.5 MB/s on the standard (IBM-defined) I/O interface or 6 MB/s on the Hitachi-specified I/O interface.

# 1.7.9 Open Systems Connection Feature

Open Systems Connection Feature (OCF) provides connectivity and interoperability to a variety of defacto-standard local area network (LAN) such as Ethernet LAN, fiber distributed data interface (FDDI) LAN, or asynchronous transfer mode (ATM) LAN, and wide area network (WAN) for the F-7C Base Models, the F-7C Turbo Models, and the F-7E Turbo Models. OCF aids in deriving the benefits of client/server computing while achieving improved connectivity throughout the enterprise.

#### 1.7.10 Console Support Including GUI and Security

Console support includes the following features:

- Console Integration (F-7C Base, F-7C Turbo, and F-7E Turbo only)

- Graphical user interface (GUI)

- Console Device (CD)

- Hardware Management Console (HMC) connectivity (optional)

- Remote Console

- · Customer-administered security

# 1.7.11 RAS Approach to Non-Stop Computing

#### Reliability

Reliability is assured with minimal physical components and connection points.

## **Availability**

Characteristics supporting system availability include:

- Concurrent channel upgrades

- Concurrent maintenance of channels, power supplies, Refrigeration Units (F-7C Turbo and F-7E Turbo only), fans, microcode, and MLPF

- IP/SP standby

- Console Device redundancy

- Fan redundancy

- Chip alternation

- $\bullet$  N + 1 power supplies

#### Serviceability

Serviceability support functions include:

- Field-replaceable unit (FRU) identification

- Online problem diagnostics

- Auto Call

- Remote operations and downloading of firmware through support centers

- Remote operations through support centers

- Remote firmware placeholders

- Deferred maintenance for redundant components

#### CHAPTER 2 INSTRUCTION PROCESSOR AND SYSTEM PROCESSOR

#### 2.1 Processor Overview

The F-7C and F-7E processor models contain one to thirteen Instruction Processors (IPs), depending upon the model, and one System Processor (SP). Both the IP and the SP use the same architectural and hardware implementations, while the logic managing these processors and their interfaces with other system components differ. Specifically, each IP or SP is implemented on a single CMOS VLSI chip, whereas the IP and the SP provide different functions as explained below.

The IP executes operating systems and application programs. It interprets processor instructions and executes those instructions using the appropriate hardware and firmware.

The SP manages external interfaces needed by the IPs to the IOPs and the SVP. It performs the back-end portion of I/O processing by routing I/O interrupts to the IPs for processing. It also serializes IP requests to the SVP and performs asynchronous execution for special IP instructions.

To summarize the foregoing, the SP performs the following general functions:

- Instruction execution for the back-end of I/O, asynchronous Expanded Storage access, and DIAGNOSE and SERVICE CALL instructions

- I/O interrupt routing

- Reset operations and SVP frame operations

- System check handling for failure detection, logout, and failure recovery

# 2.2 System Processor Interface Design and Function

When an IP needs to interface with an IOP or the SVP during instruction processing, it interfaces directly with the SP instead. The SP in turn handles the SVP and IOP interfaces. Note that the SP handles only back-end interrupts and is not involved with starting an I/O. The SP uses the following types of interfaces.

#### 2.2.1 Interface between SP and IP

- SP to IP(s): This interface uses a request table with locks in the Hardware System Area (HSA). An SP issues requests to an individual IP or to all IPs (as in failure situations) and updates the HSA request table. When the IP processes the signal using the request table, it either handles the request or has the SP execute the required action for the IP.

- IP to SP: This interface uses a request table with locks in the HSA. An IP issues requests to the SP via the request table. When the SP polls the table, it executes the requested action and removes the request from the table.

#### 2.2.2 SVP Interface

This interface uses a four byte read/write register and service word protocol. Both the SVP and SP pass requests back and forth using the register.

The SP uses this interface for tasks such as DIAGNOSE, SERVICE CALL, and HYPERVISOR CALL instructions and for performing status report and logout requests.

The SVP uses this interface for tasks such as maintenance functions and reset, and to indicate the end of a required instruction such as END OF DIAGNOSE or SERVICE SIGNAL.

#### 2.2.3 IOP Interface

- IOP to SP: The IOP uses an attention request mechanism to report interruptions of I/O completions or errors. Or, a control interface is used to set/reset hardware registers which enable/disable IOP attention.

- IOP to SP to IP: The SP is not used to start I/O activity but instead routes back-end I/O interruptions to the appropriate IPs. The SP generates interruptions by sending I/O interrupt requests to the IP.

#### 2.3 Address Translation Process with Lookaside Buffers

Accessing instructions and data in main storage requires translating virtual addresses into real addresses, which is accomplished by the dynamic address translation (DAT) mechanism.

Address translation tables architecturally reside in main storage, however, and main storage accesses can degrade performance even with sophisticated cache mechanisms. The F-7C and F-7E processor models therefore contain two types of lookaside buffers to help prevent main storage accesses for address translation. When an address to be translated is found in these buffers, access to the main storage translation tables is bypassed.

#### 2.3.1 Virtual Address Formats

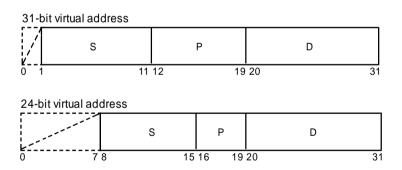

The F-7C and F-7E processor models support 31-bit and 24-bit addressing of main storage under program control. Formats are shown in figure 2-1.

- S: Segment field. Specifies the entry in the segment table.

- P: Page field. Specifies the entry in the page table.

- D: Displacement field. Specifies the address within the page.

Figure 2-1 Examples of Virtual Address Formats

# 2.3.2 Address Translation Using Translation Lookaside Buffer

Each IP and SP has a Translation Lookaside Buffer (TLB) to accelerate translating virtual addresses into real addresses. The TLBs hold virtual-to-real address pairs translated by the dynamic address translation (DAT) facility. The reuse of entries held in the TLB allows the full DAT process (storage access of segment and page tables) to be bypassed, thus improving overall system performance.

The TLB uses high-speed array chips to provide high performance and can hold up to 256 virtual-real address pairs. The TLB employs a set-associative addressing structure. Lines in the TLB are replaced by the least recently used (LRU) algorithm.

If the TLB does not contain the sought-after valid virtual-real address pair, the DAT process, which makes use of control register contents, segment tables, and page tables, translates the virtual address into the real address. The following description explains these address translation steps, including the registration of the translated virtual-real address pairs in the TLB.

- 1. Adds the value in the segment field of the virtual address to the segment table origin address stored in either control register 1 or 7, depending upon whether the address space is primary or secondary.

- 2. References the segment table using the address derived in step 1.

- 3. Adds the value in the page field of the virtual address to the page-table-origin address found in the segment table entry.

- 4. References the page table using the address derived in step 3.

- 5. Obtains the real page frame address.

- 6. Converts the real page frame address into the absolute page address by prefixing and by concatenating the value in the displacement field of the virtual address to the right of the absolute page frame address.

- 7. Registers into the TLB the pair of the segment and page fields of the virtual address and the absolute page address.

As part of the address translation process, the lengths of the segment and page tables and the entries in these tables are checked for validity. If any errors are found, an address translation exception is recognized and a program interruption is generated.

#### 2.3.3 Address Translation Using Access Register

Each IP and SP has an ART Lookaside Buffer (ALB) to accelerate translating virtual addresses into real addresses. This translation process is called access register translation (ART).

In ESA mode, data in any space can be referenced by an access register with the base register field of the instruction. For example, in a sequence where a MOVE CHARACTER instruction (MVC) in the address space selects target data using an access register (access register translation), the following takes place:

- 1. The base register field of the instruction designates an access register.

- 2. The value in the selected access register is added to the access list origin address, and the result selects an entry from the access list.

- 3. The access list entry refers to a control table.

- 4. The segment table origin designated by the control table selects a target data space.

- 5. The target data address in the data space is obtained as a virtual address.

- 6. The virtual address of the target data address is translated to a real address by conventional dynamic address translation using the segment table origin in the virtual address.

In this translation process, the segment table origin is obtained through two levels of conversion: access list and control table, which are both maintained in main storage. If such reference to main storage occurs at every translation, the translation speed remains relatively low. To improve this, the ALB is implemented in the IP and the SP as a dedicated lookaside buffer for access register translation allowing the translation process to bypass two main storage references.

# 2.4 Pipeline Design and Features

The F-7C and F-7E processor models use pipelines for instruction execution. This pipeline operates in overlap mode so it is able to have a different instruction at each stage of the pipeline and complete an instruction once every system cycle.