# ABCs of z/OS System Programming Volume 10

Redbooks

# International Technical Support Organization

# ABCs of z/OS System Programming Volume 10

September 2008

| <b>Note:</b> Before using this information and the product it supports, read the information in "Notices" on page xi.                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

|                                                                                                                                                             |

| Fourth Edition (September 2008)                                                                                                                             |

| This edition applies to Version 1 Release 10 of z/OS (5694-A01) and to all subsequent releases and modifications until otherwise indicated in new editions. |

|                                                                                                                                                             |

|                                                                                                                                                             |

# **Contents**

| Notices                                                |      |

|--------------------------------------------------------|------|

| Trademarks                                             | xii  |

| Preface                                                | yiii |

| The team that wrote this book                          |      |

| Become a published author                              |      |

| Comments welcome                                       |      |

|                                                        |      |

| Chapter 1. Introduction to z/Architecture              |      |

| 1.1 Computer architecture overview                     |      |

| 1.2 Concept of a process                               |      |

| 1.3 Process states and attributes                      |      |

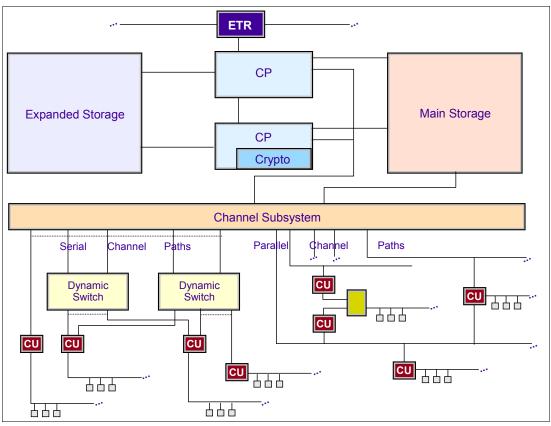

| 1.4 System components                                  |      |

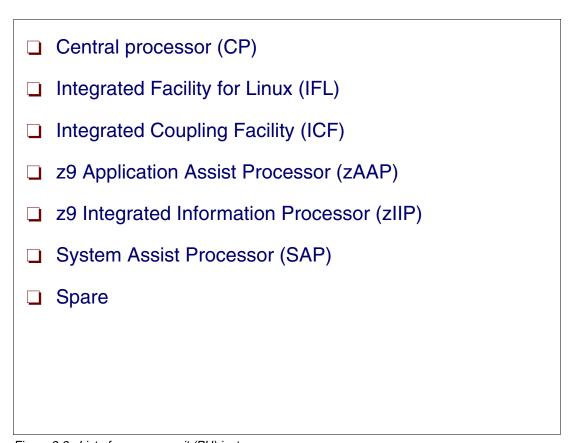

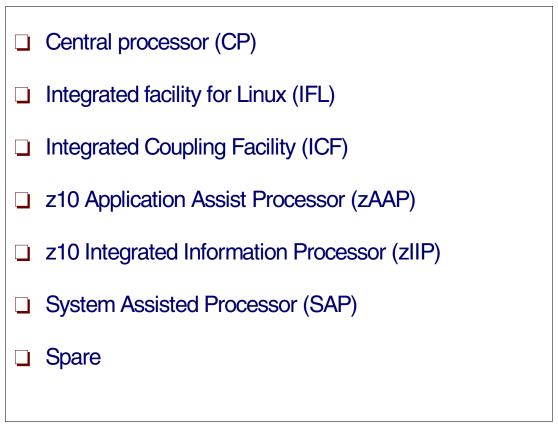

| 1.5 Processing units (PUs)                             |      |

| 1.6 z/Architecture enhancements                        |      |

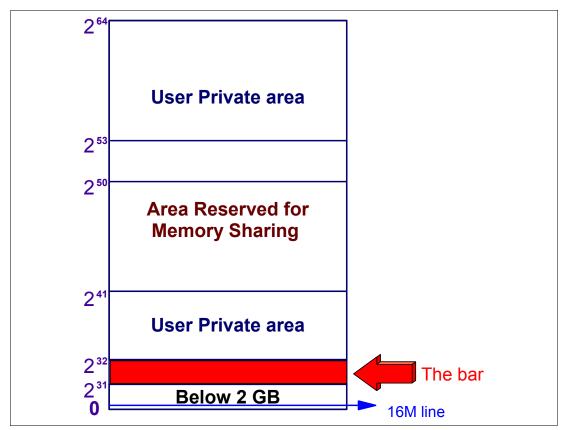

| 1.7 64-bit address space map                           |      |

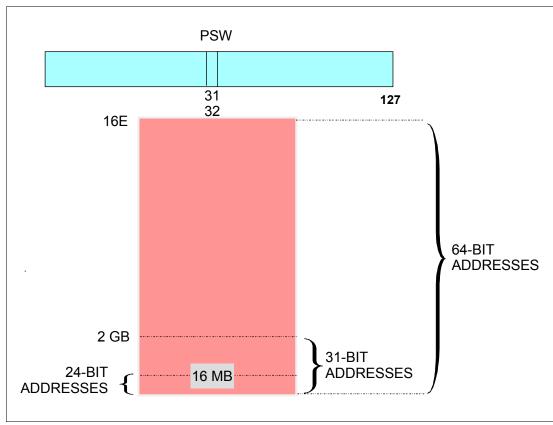

| 1.8 Addressing mode                                    |      |

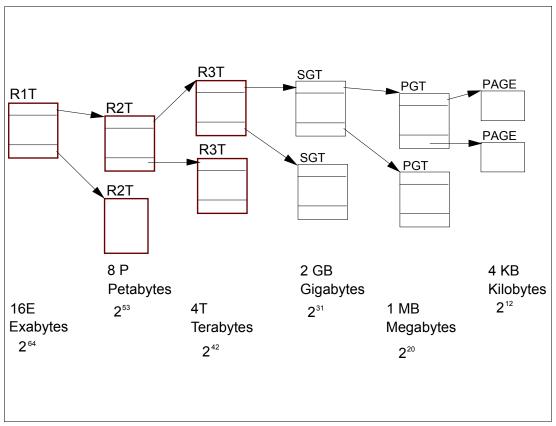

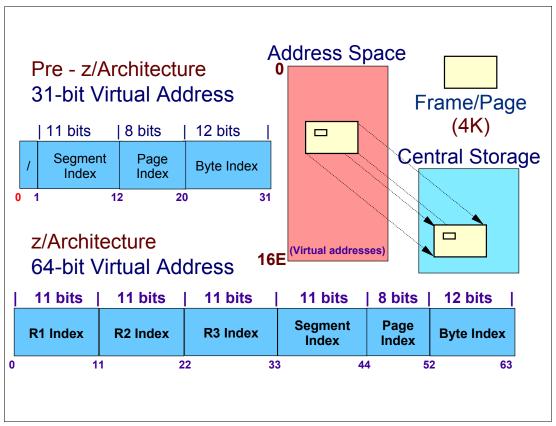

| 1.9 64-bit dynamic address translation                 |      |

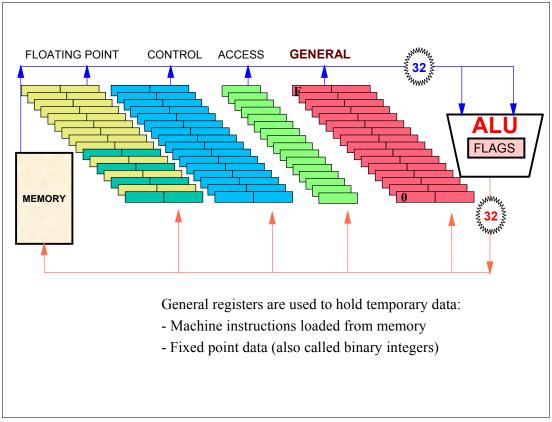

| 1.10 CP registers (general)                            |      |

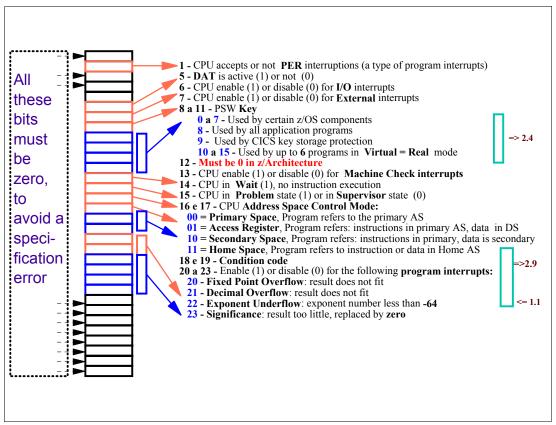

| 1.12 Current program-status word (PSW)                 |      |

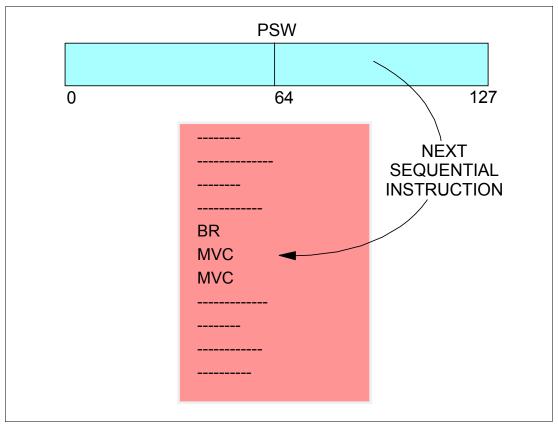

| 1.13 Next sequential instruction address               |      |

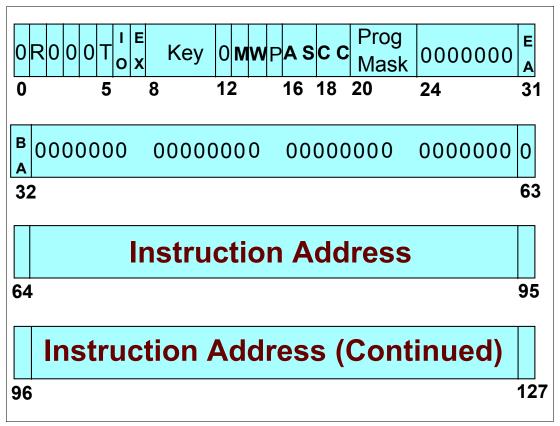

| 1.14 Program-status-word format                        |      |

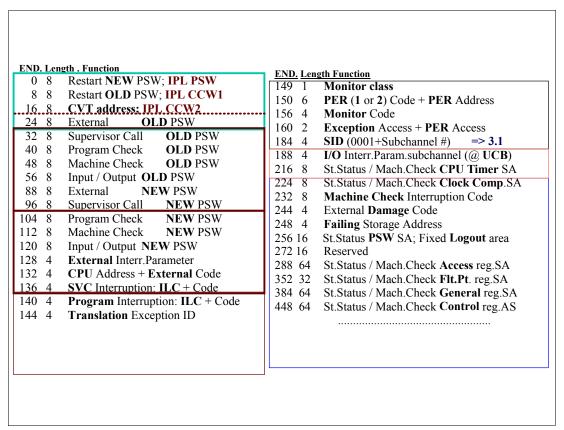

| 1.15 Prefixed save area (PSA)                          |      |

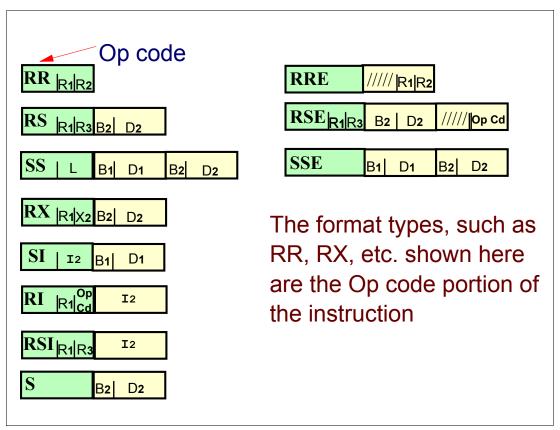

| 1.16 Several instruction formats                       |      |

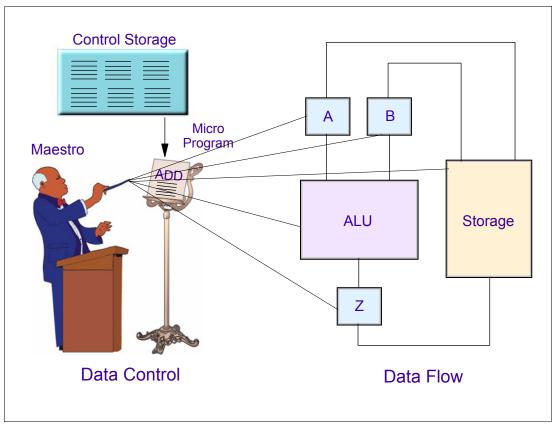

| 1.17 Microcode concepts                                |      |

| 1.18 z/Architecture components                         |      |

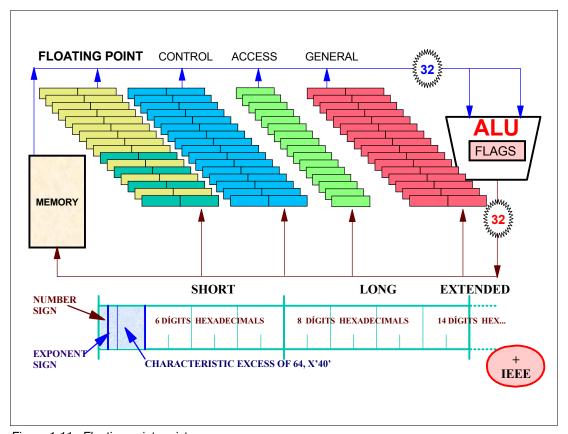

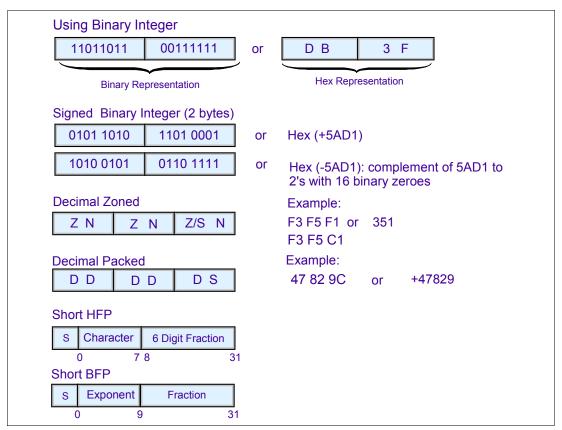

| 1.19 z/Architecture data formats                       |      |

| 1.20 Interrupts                                        |      |

| 1.21 Interrupt processing                              |      |

| 1.22 Types of interrupts                               |      |

| 1.23 Supervisor call interrupt                         | . 40 |

| 1.24 Storage protection                                |      |

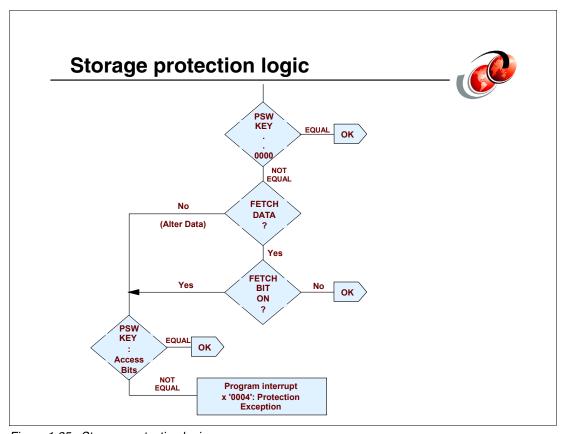

| 1.25 Storage protection logic                          | . 45 |

| 1.26 Addresses and address spaces                      |      |

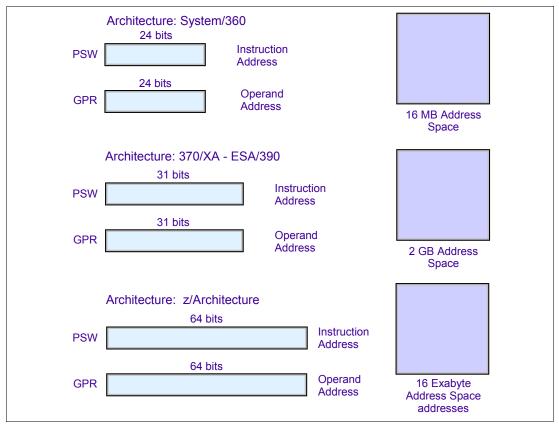

| 1.27 z/Architecture address sizes                      |      |

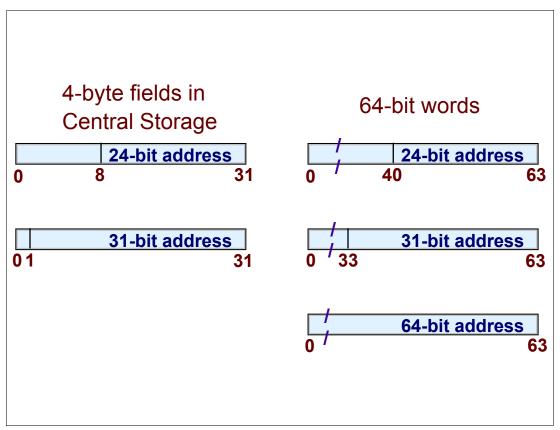

| 1.28 Storage addressing                                | . 49 |

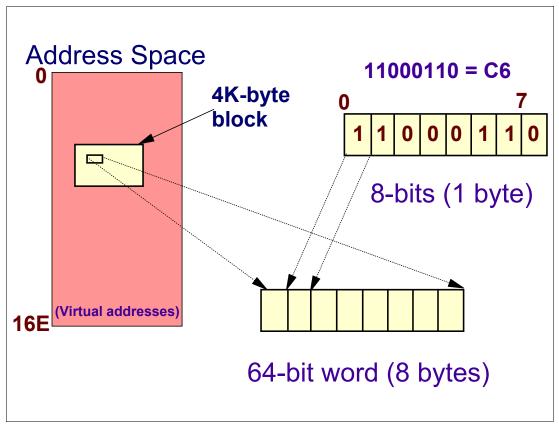

| 1.29 Real storage locations                            |      |

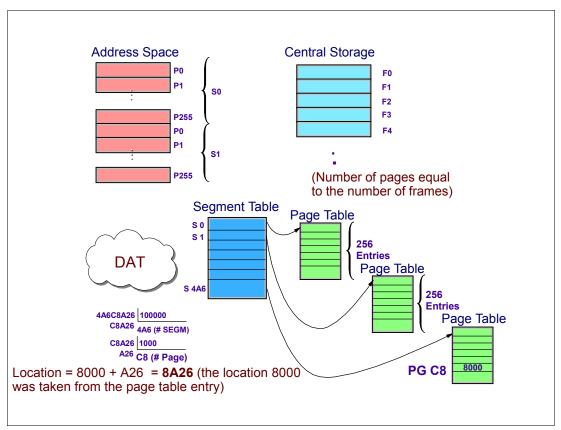

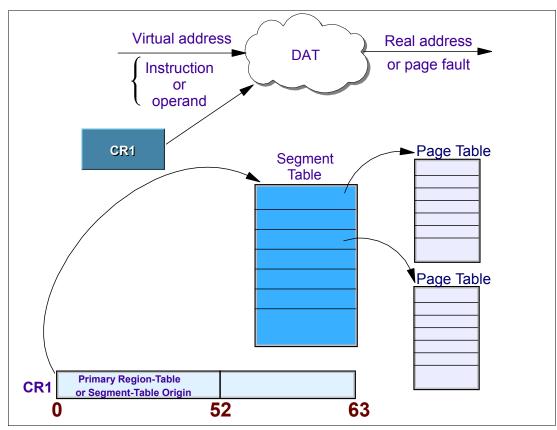

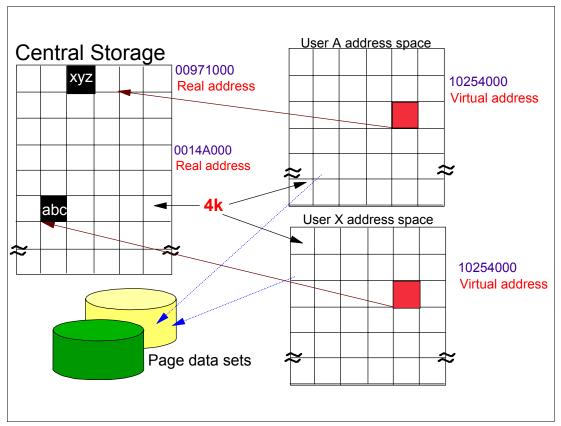

| 1.30 Dynamic address translation (DAT)                 | . 52 |

| 1.31 Dynamic address translation                       |      |

| 1.32 Page faults                                       |      |

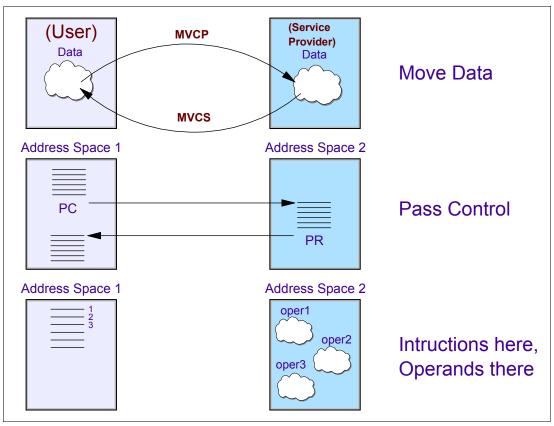

| 1.33 Dual address space (cross memory)                 |      |

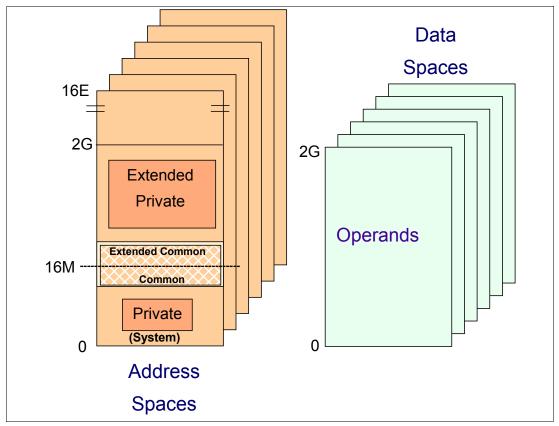

| 1.34 Access register mode (dataspaces)                 |      |

| 1.35 CPU signaling facility                            |      |

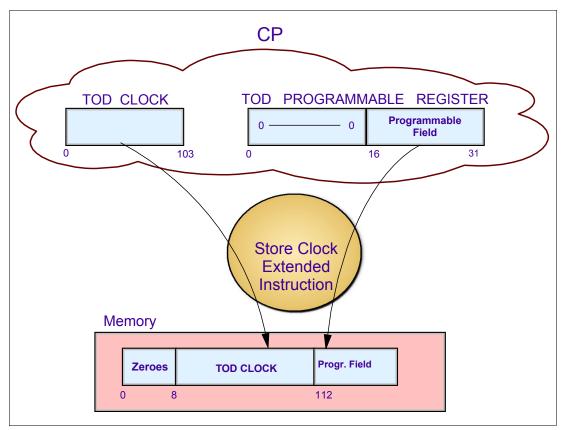

| 1.36 Time measurement TOD.                             |      |

| 1.37 Time measurement (CP timer)                       |      |

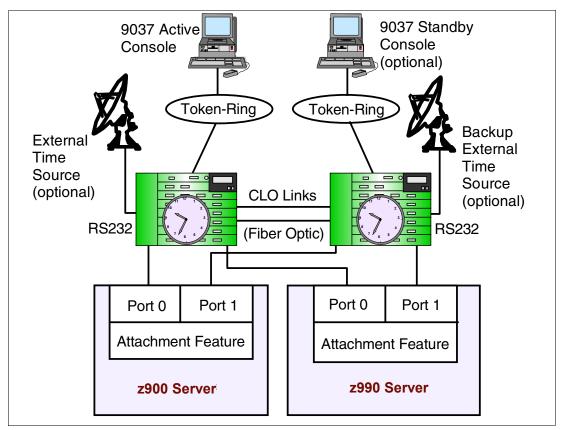

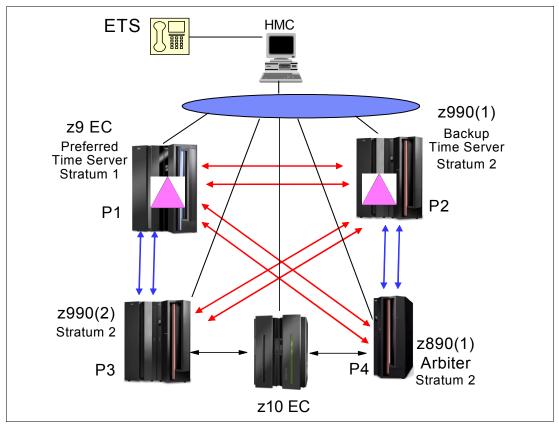

| 1.38 Sysplex Timer expanded availability configuration |      |

| 1.39 Server Time Protocol (STP)                        |      |

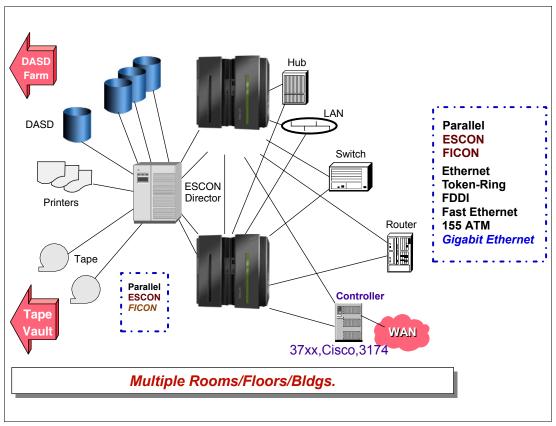

| 1.40 Data center and I/O configuration                 | . 69 |

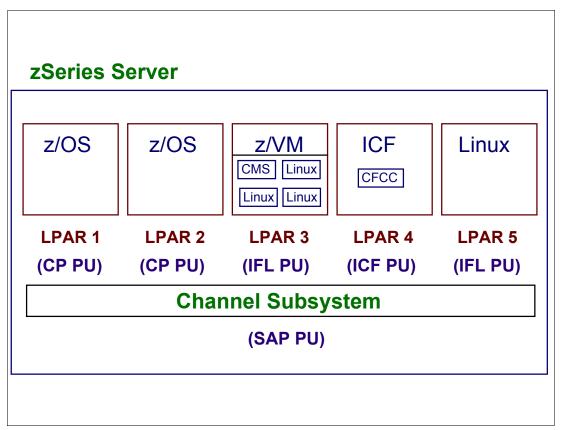

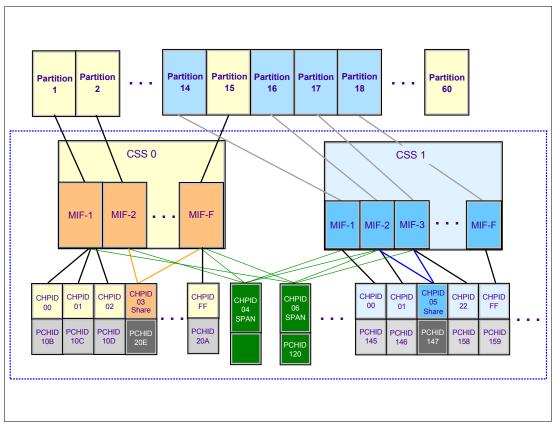

| 1.41 Channel subsystem                         | 71  |

|------------------------------------------------|-----|

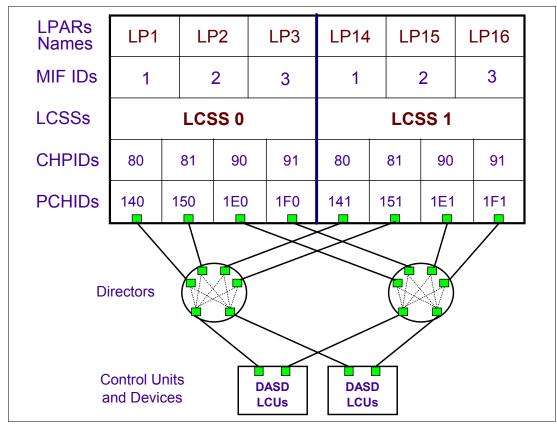

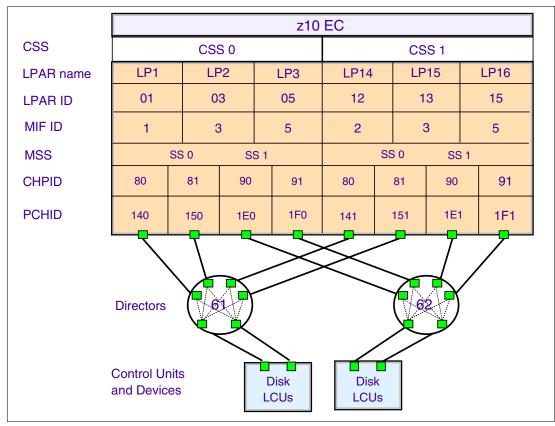

| 1.42 Multiple CSS structure (z10 EC)           |     |

| 1.43 Control units                             |     |

|                                                |     |

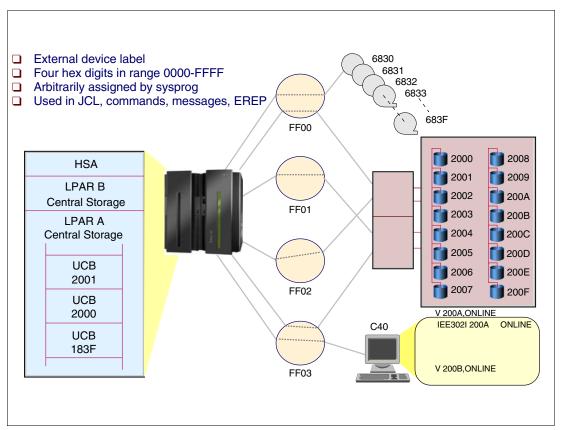

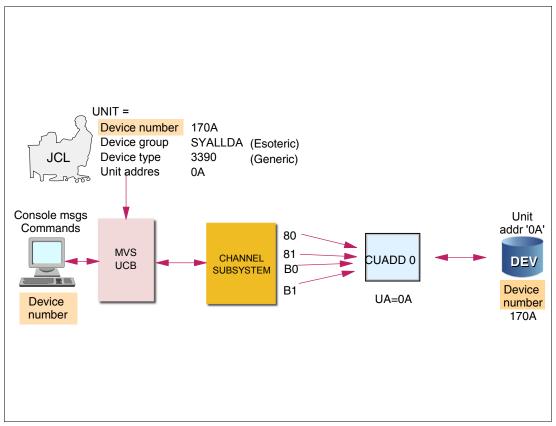

| 1.44 Device number                             |     |

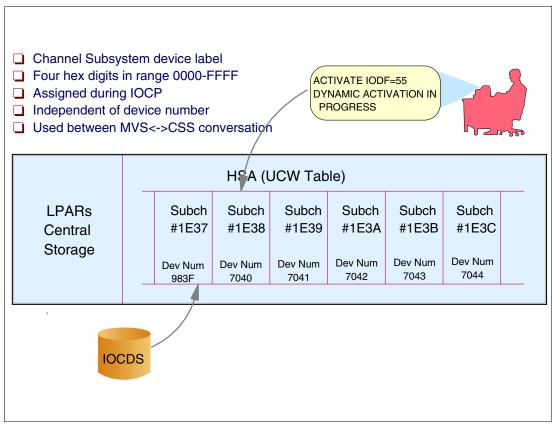

| 1.45 Subchannel number                         |     |

| 1.46 Subchannel numbering                      |     |

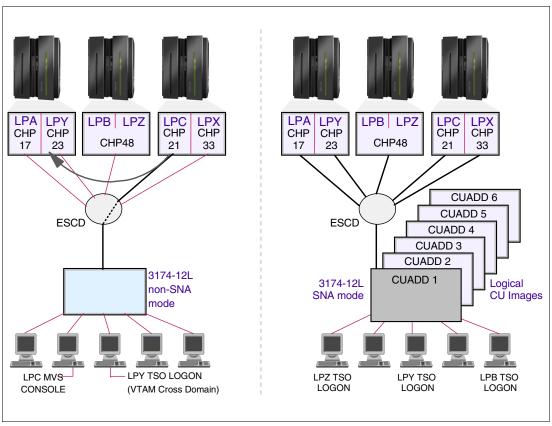

| 1.47 Control unit address                      |     |

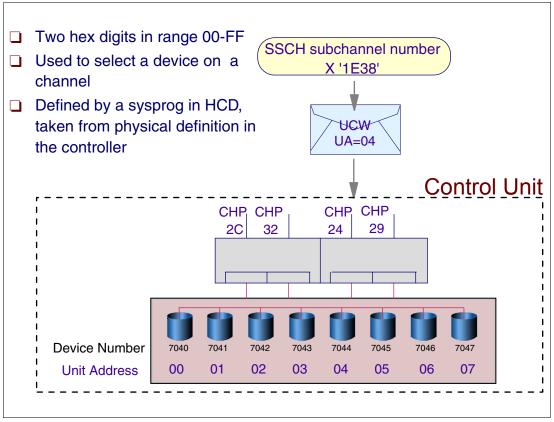

| 1.48 Unit addresses                            |     |

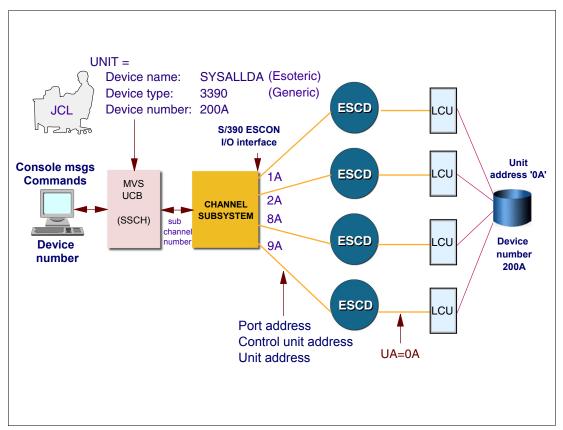

| 1.49 Map device number to device address       |     |

| 1.50 Multiple channel paths to a device        |     |

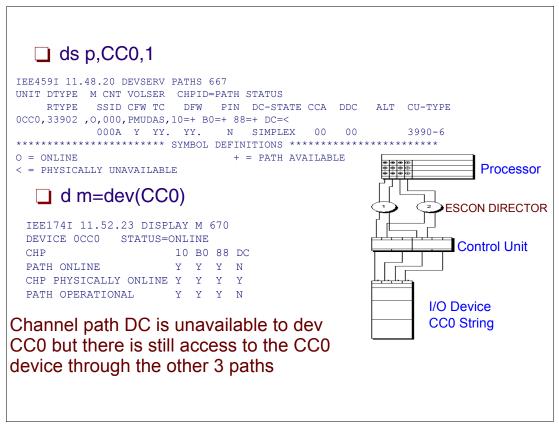

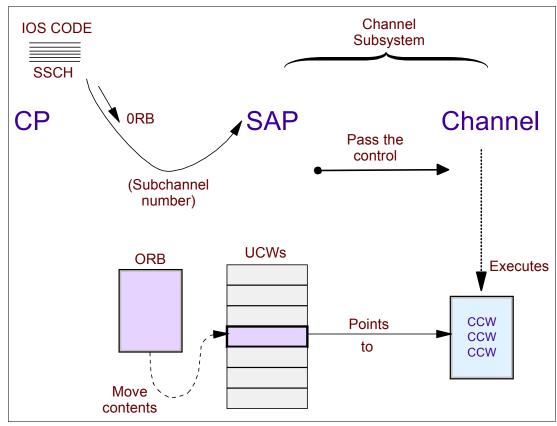

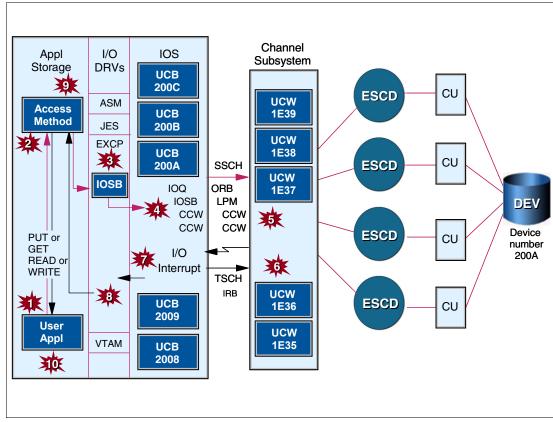

| 1.51 Start subchannel (SSCH) logic             | 90  |

| 1.52 SAP PU logic                              | 92  |

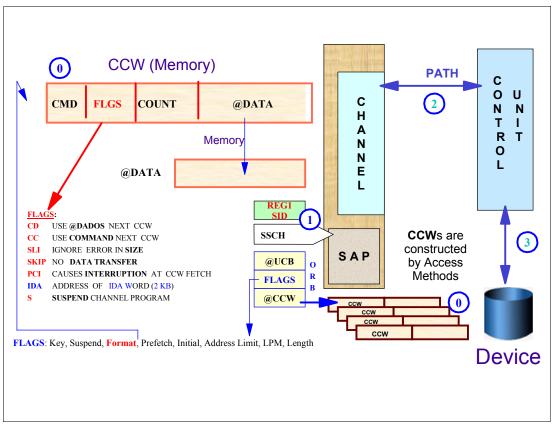

| 1.53 Channel processing                        | 94  |

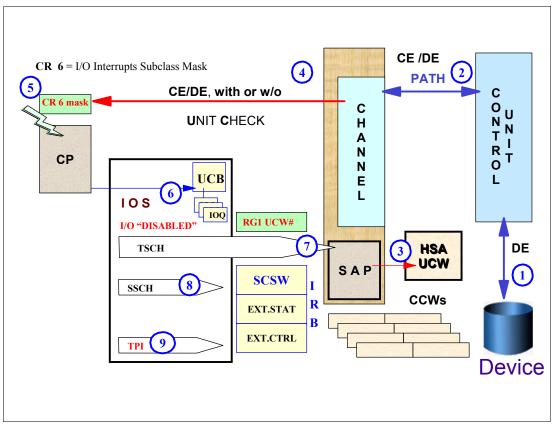

| 1.54 I/O interrupt processing                  | 96  |

| 1.55 I/O summary                               |     |

| ,                                              |     |

| Chapter 2. IBM System z                        | 101 |

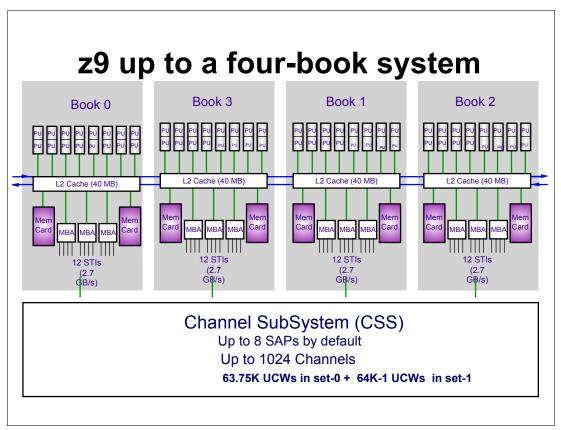

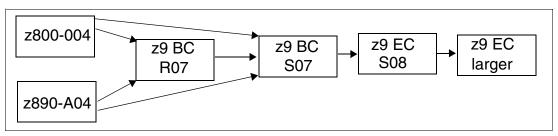

| 2.1 z9 EC models overview                      | 103 |

| 2.2 z9 BC models overview                      | 105 |

| 2.3 Processor unit (PU) instances              |     |

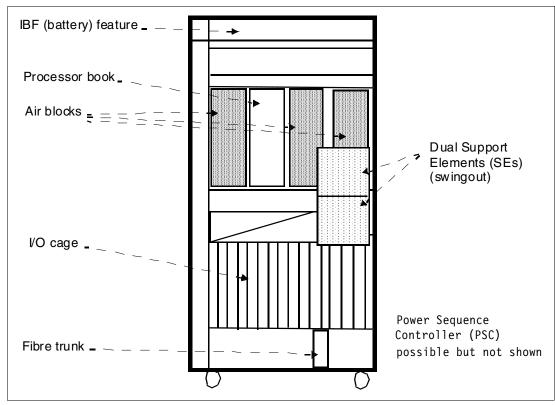

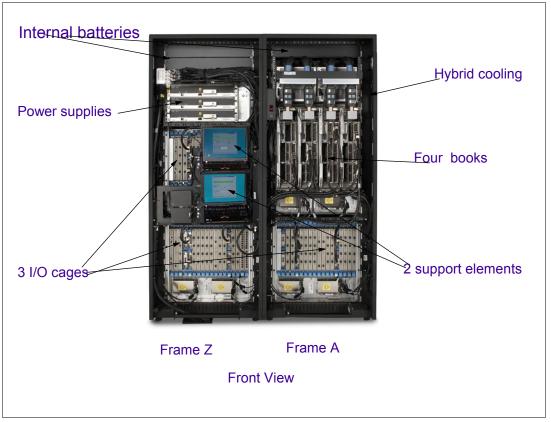

| 2.4 z9 EC frames and cages                     |     |

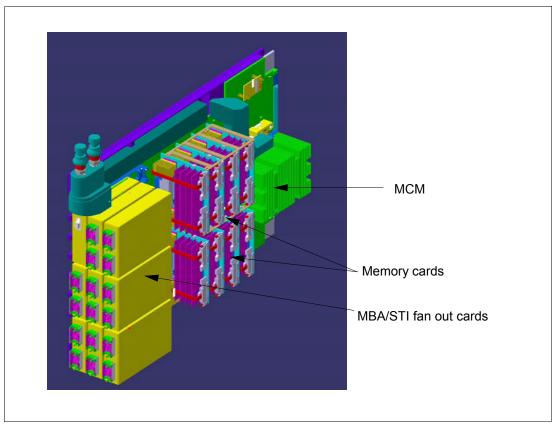

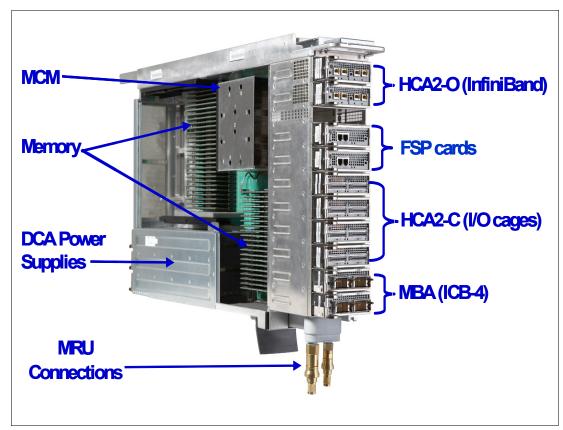

| 2.5 PU cage and books                          |     |

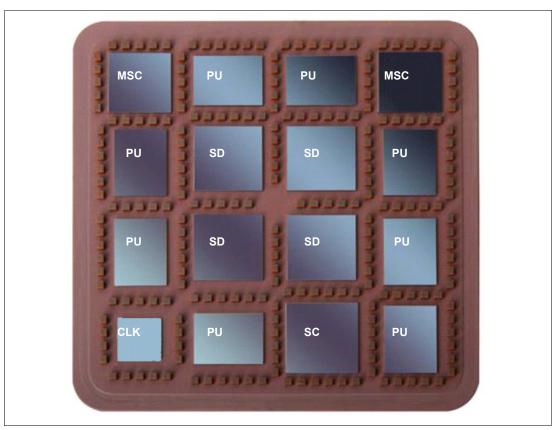

| 2.6 z9 EC Multichip module (MCM)               |     |

| 2.7 Pipeline in z9 EC                          |     |

| ·                                              |     |

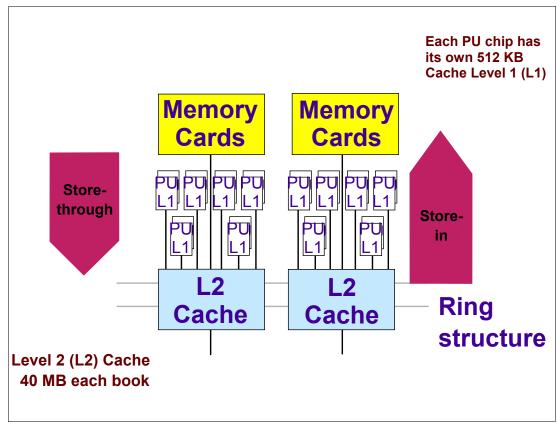

| 2.8 Processor unit caches                      |     |

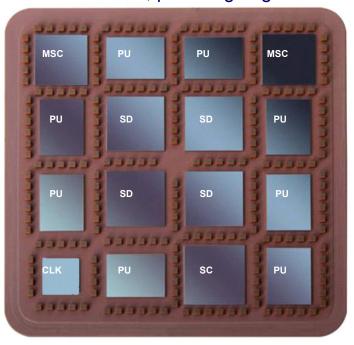

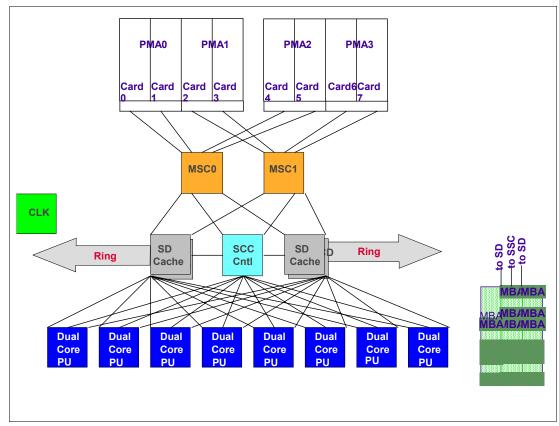

| 2.9 Cache and PU, SC, SD, and MSC chips        |     |

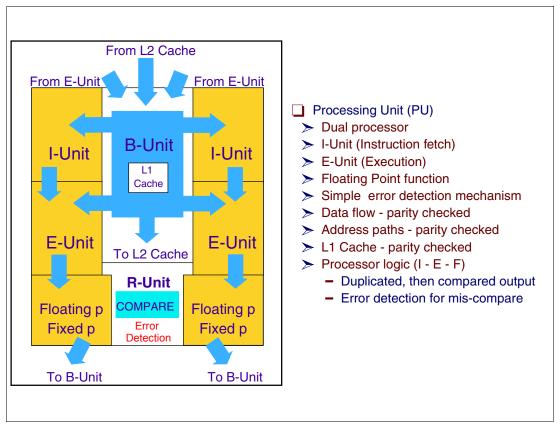

| 2.10 Instruction and execution units           |     |

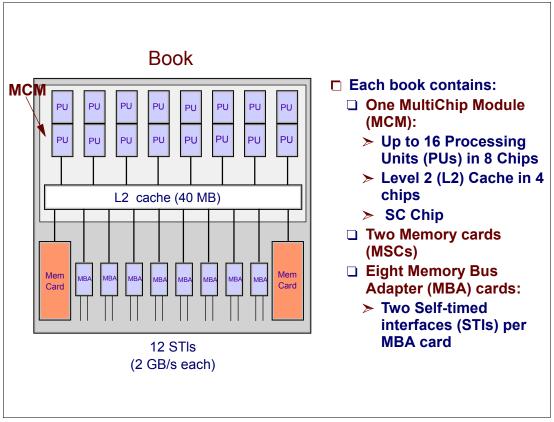

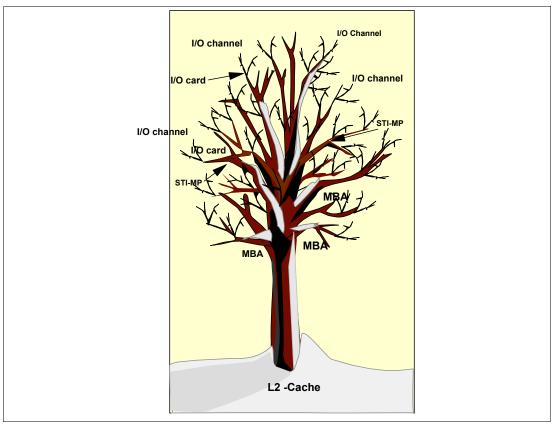

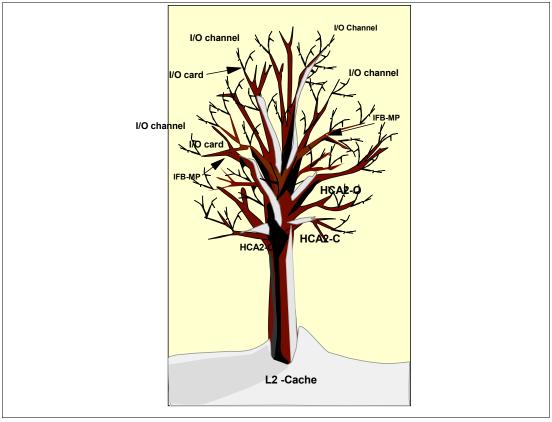

| 2.11 A book (logical view)                     |     |

| 2.12 Physical book design                      |     |

| 2.13 L2 cache and book connection              |     |

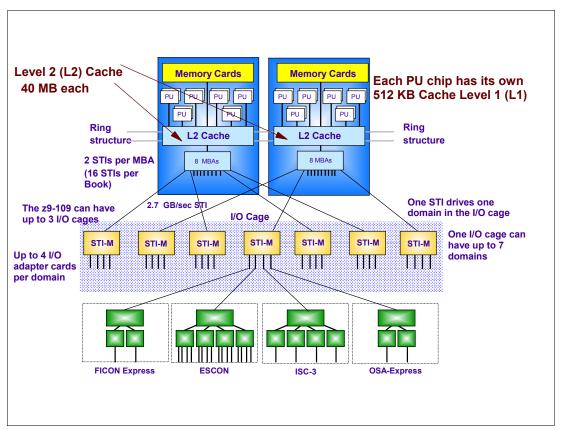

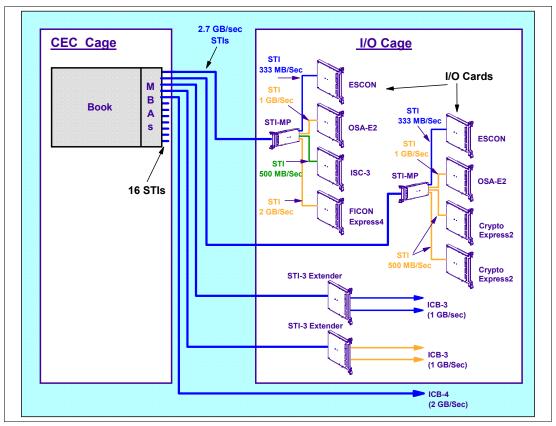

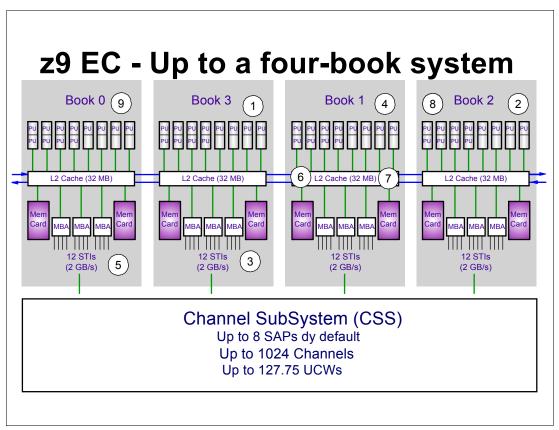

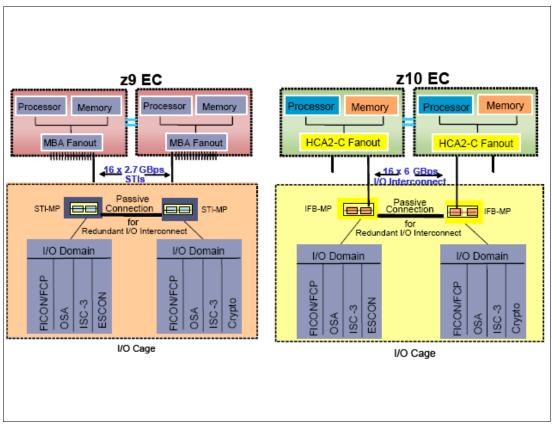

| 2.14 Self-timed interconnect (STI) and domains |     |

| 2.15 STIs and I/O cards                        | 128 |

| 2.16 The I/O data flow                         | 129 |

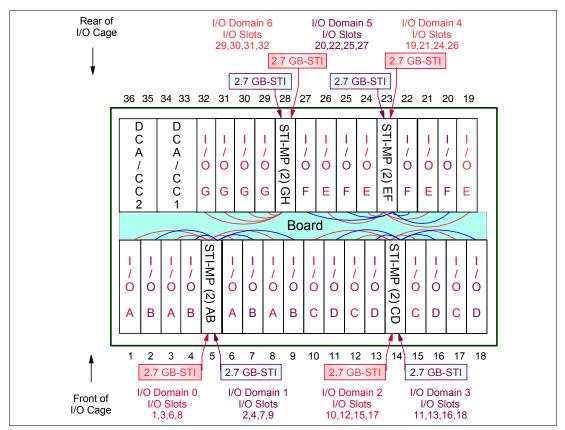

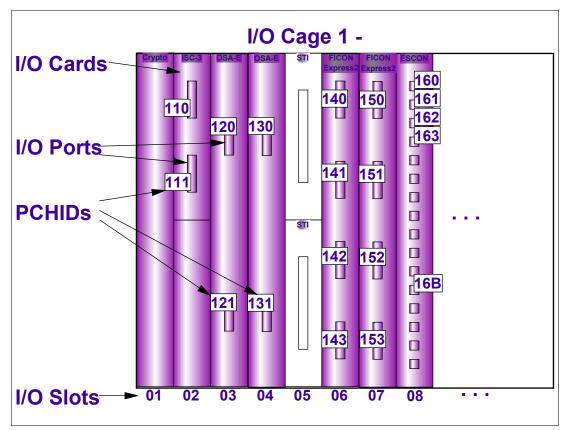

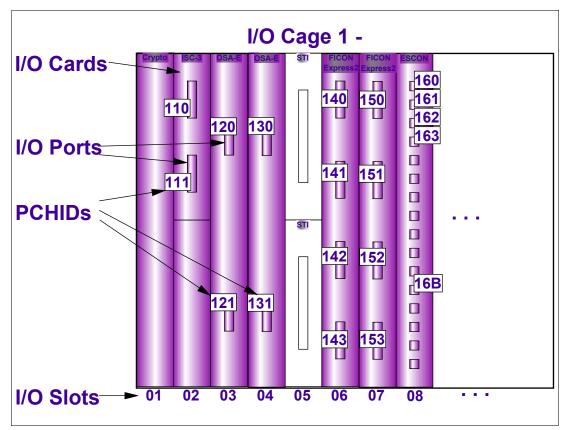

| 2.17 z9 EC I/O cage                            | 130 |

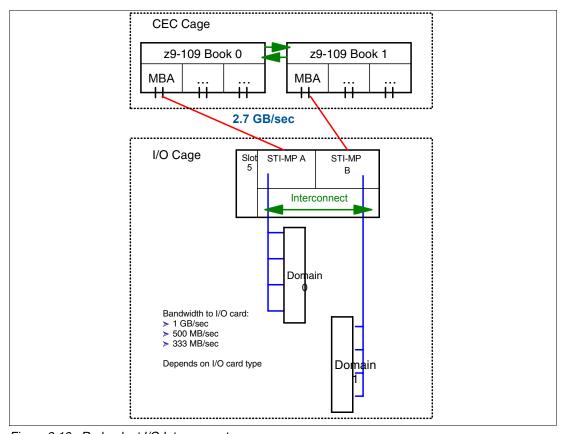

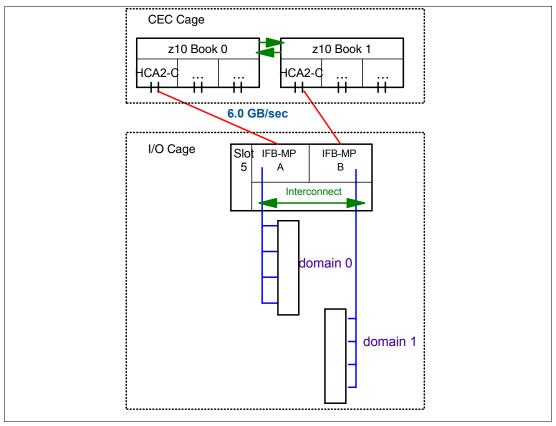

| 2.18 Redundant I/O Interconnect                | 132 |

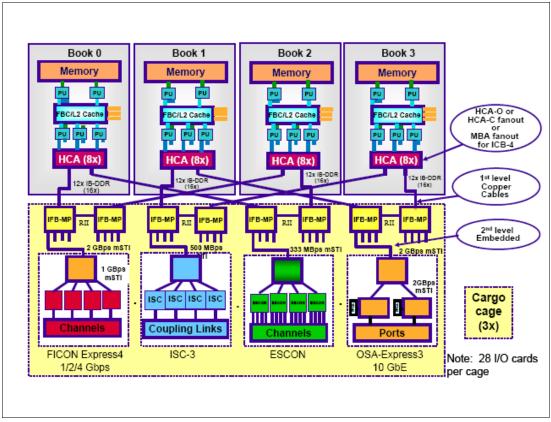

| 2.19 I/O operation in a multi-book server      |     |

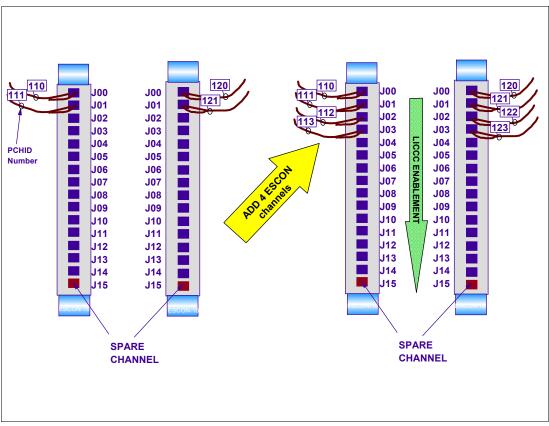

| 2.20 16-port ESCON channel card                |     |

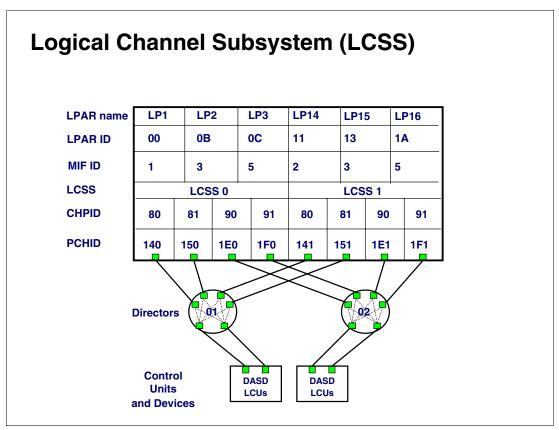

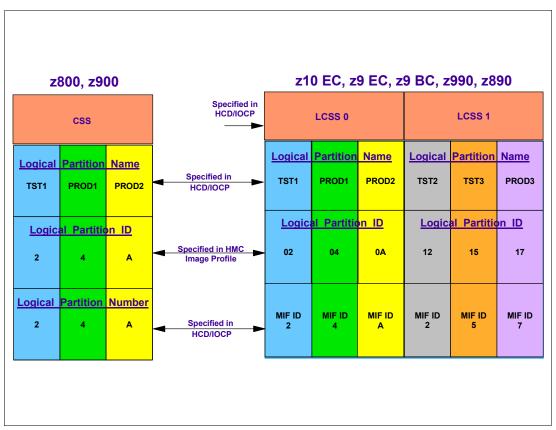

| 2.21 Logical Channel Subsystem (LCSS)          |     |

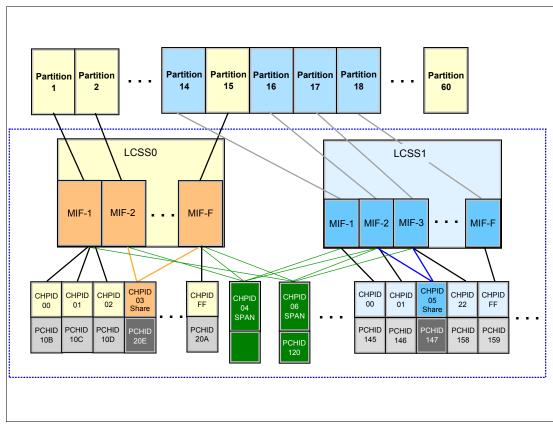

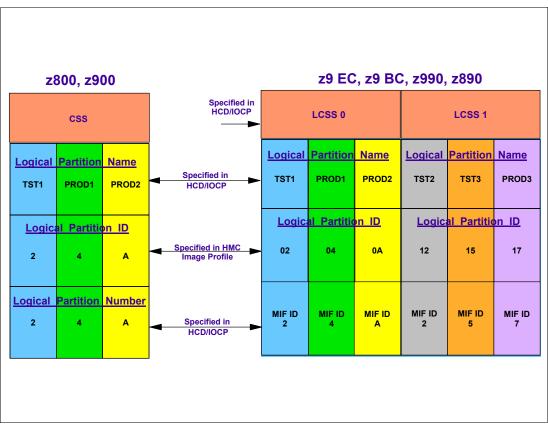

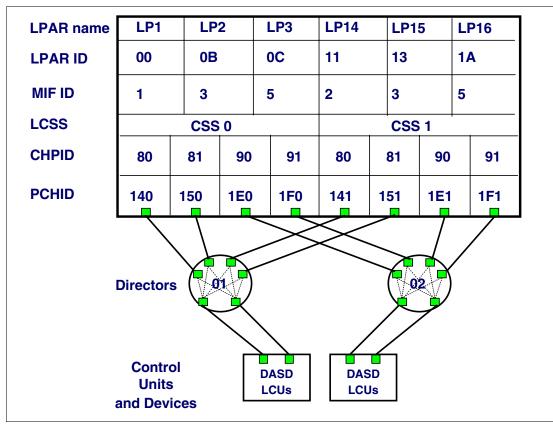

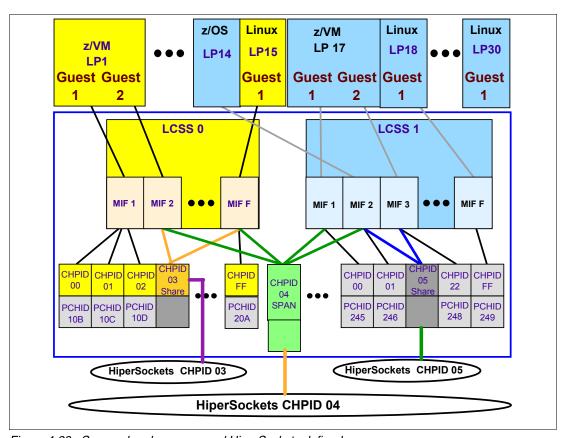

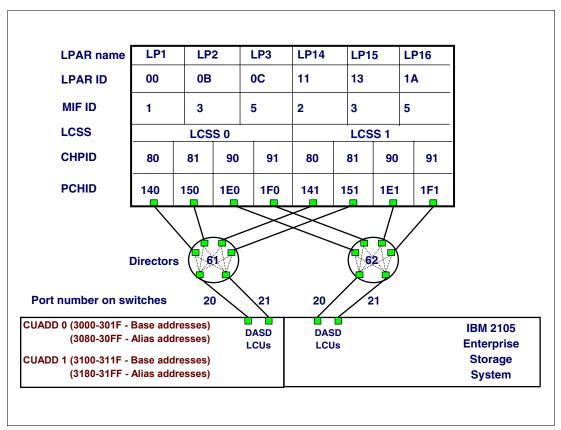

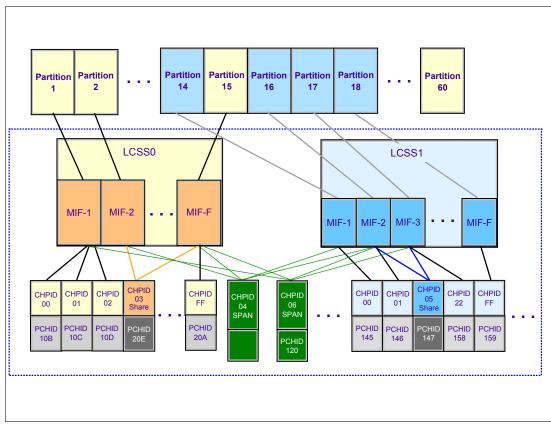

| 2.22 LP IDs, MIF IDs and spanning concepts     |     |

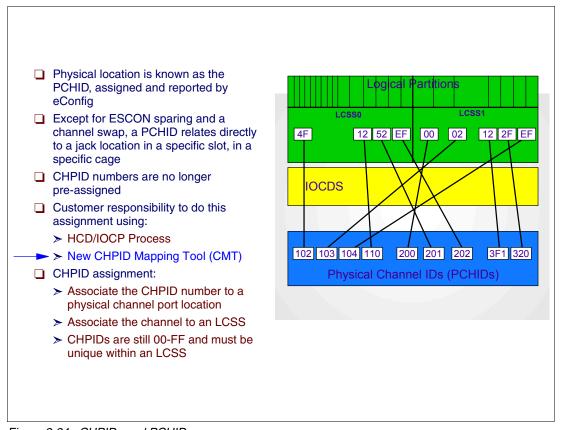

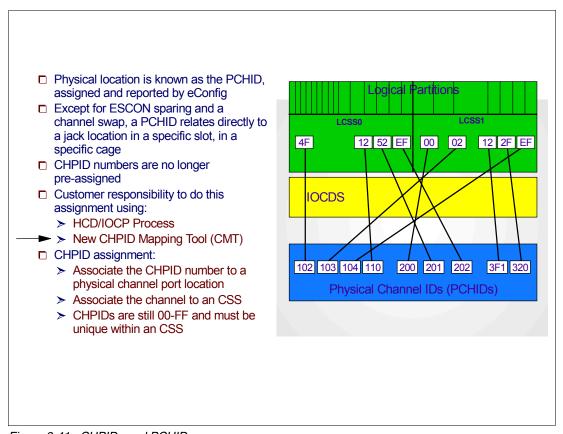

| 2.23 Physical channel ID (PCHID)               |     |

| 2.24 Association between CHPIDs and PCHIDs     |     |

|                                                |     |

| 2.25 Comparison between System z servers       |     |

| 2.26 IOCP statements example                   |     |

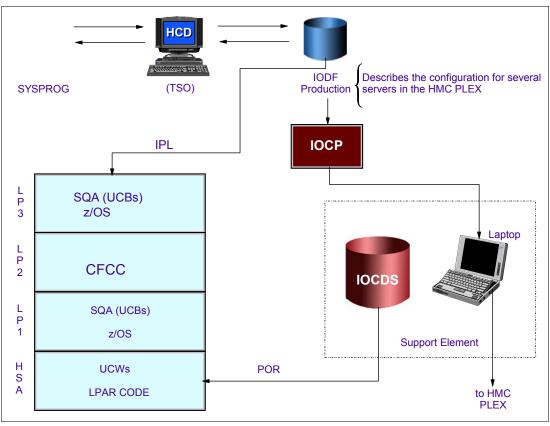

| 2.27 Configuration definition process          |     |

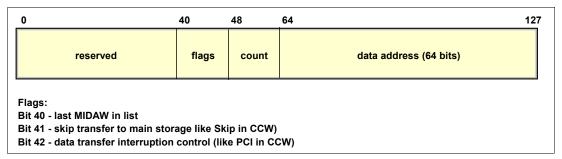

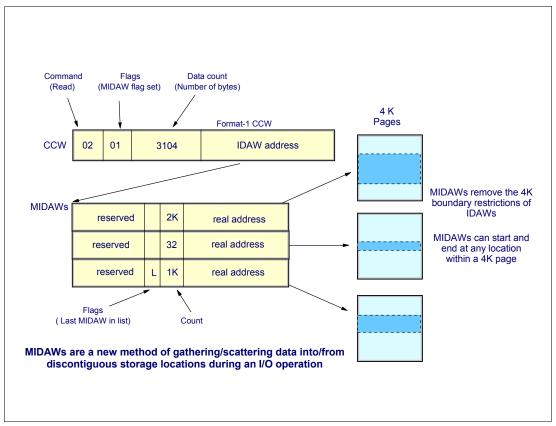

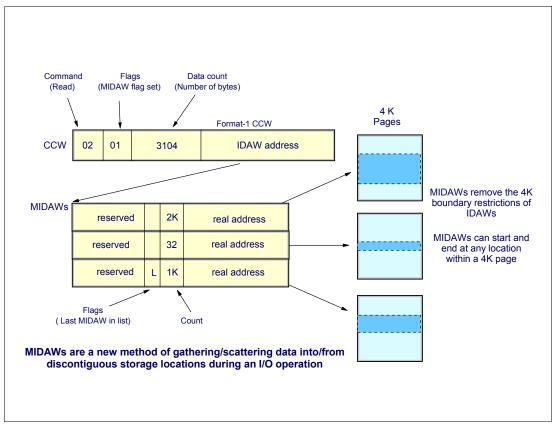

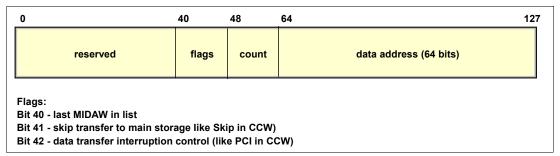

| 2.28 Introduction to MIDAW                     |     |

| 2.29 Using MIDAWs                              |     |

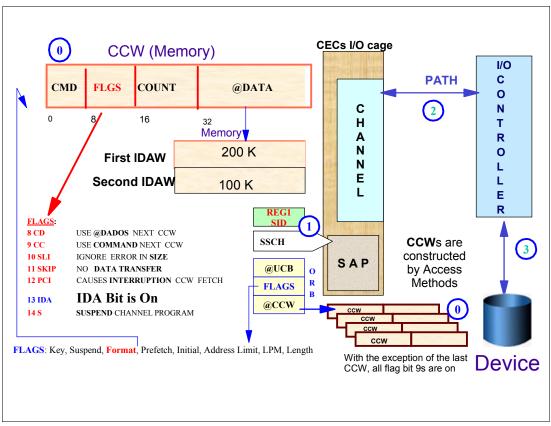

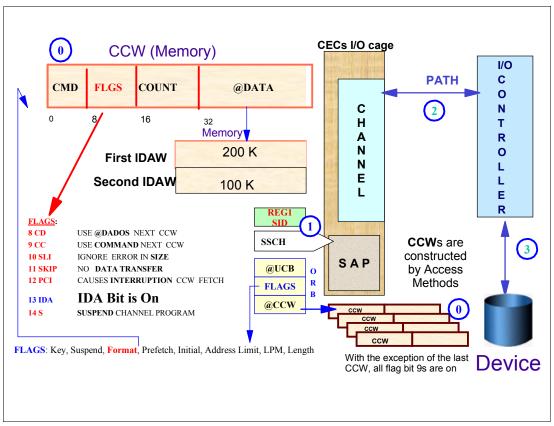

| 2.30 Channel command word (CCW) concept        |     |

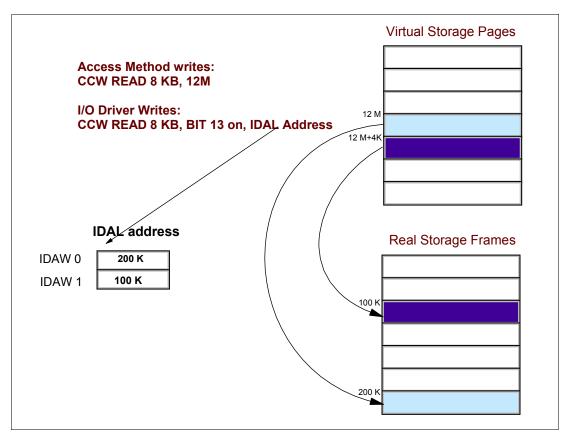

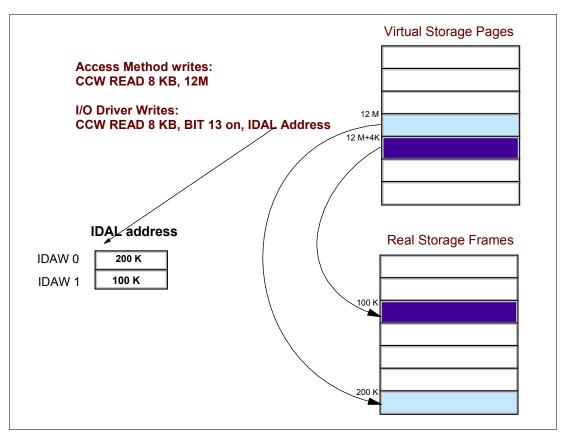

| 2.31 CCWs and virtual storage - IDAW Concept   |     |

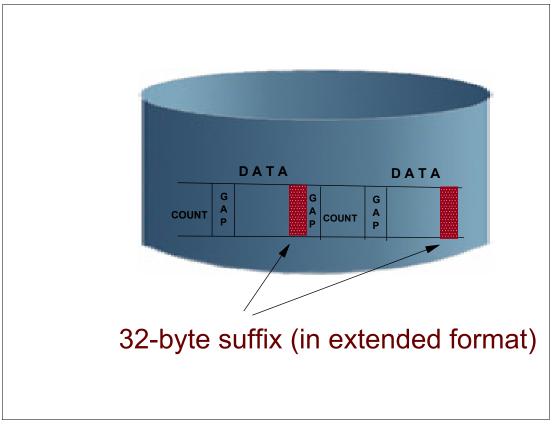

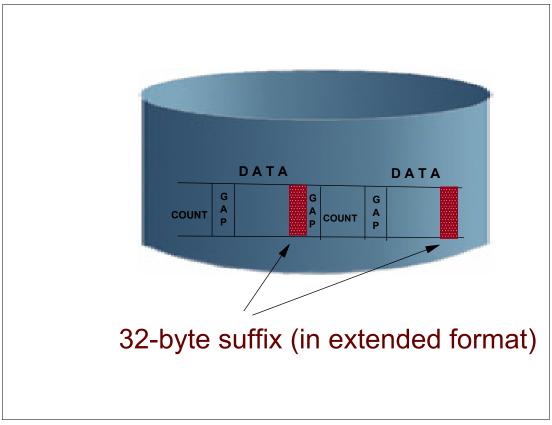

| 2.32 DASD extended format                      |     |

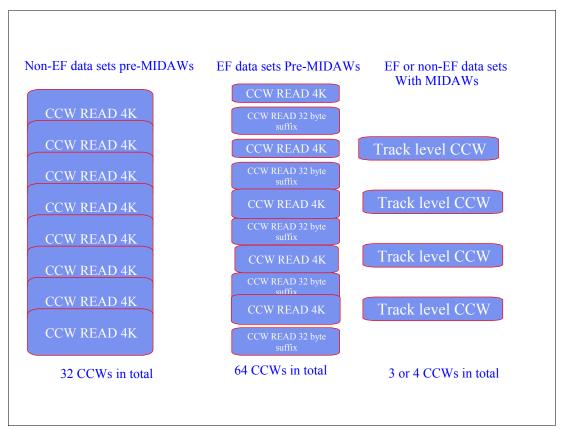

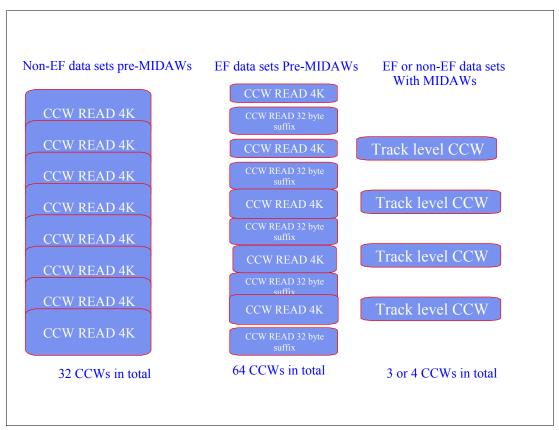

| 2.33 Reducing CCWs using MIDAW                 | 158 |

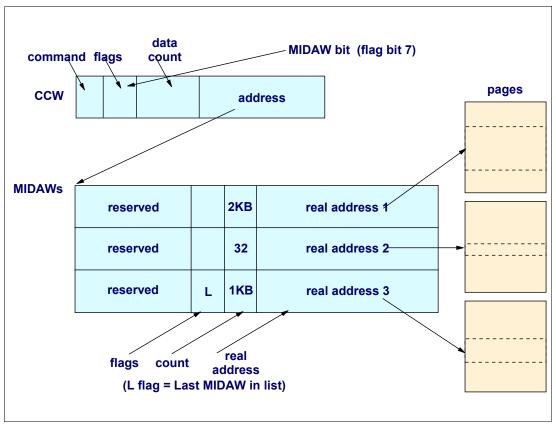

| 2.34 MIDAW facility                            |     |

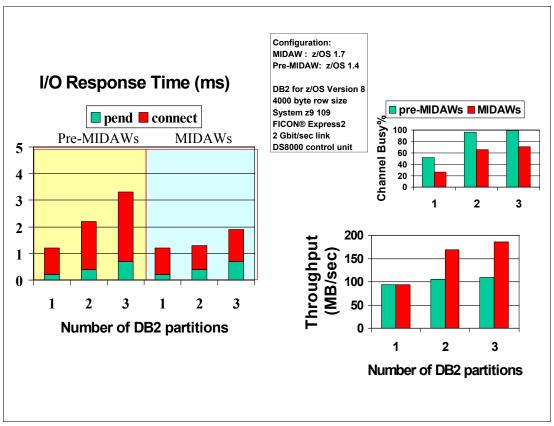

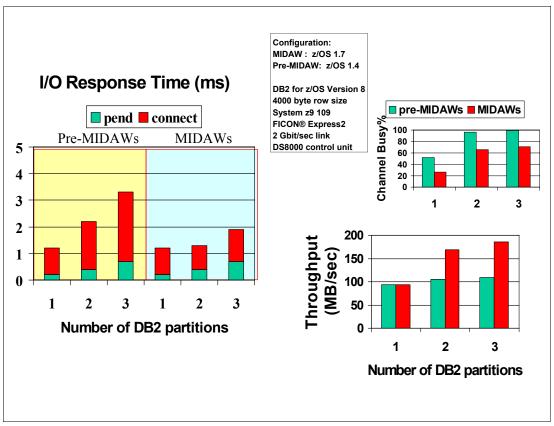

| 2.35 MIDAW performance results                 |     |

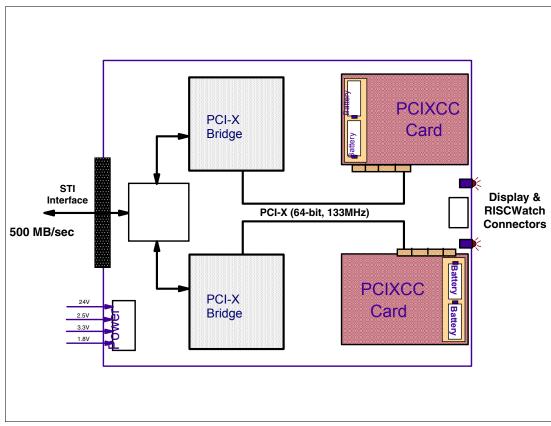

| 2.36 Cryptographic hardware features           |     |

| 2.37 Crypto Express2                       |     |

|--------------------------------------------|-----|

| 2.38 z9 EC crypto synchronous functions    | 167 |

| 2.39 z9 EC crypto asynchronous functions   | 168 |

| 2.40 Non-disruptive upgrades               | 170 |

| 2.41 z9 EC new features                    | 173 |

| 2.42 z9 BC functions and comparisons       | 176 |

| 01                                         | 470 |

| Chapter 3. IBM System z10 EC               |     |

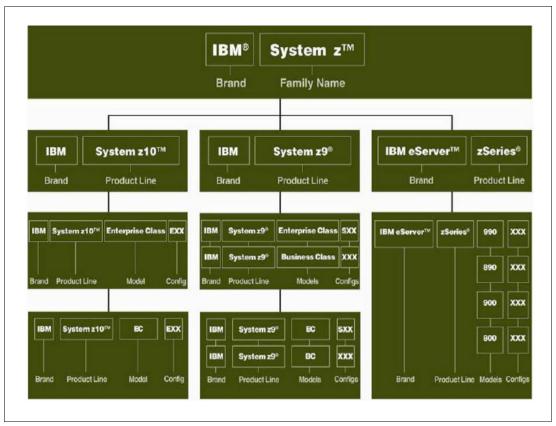

| 3.1 z10 EC overview                        |     |

| 3.2 IBM System z nomenclature              |     |

| 3.3 z10 EC naming summary                  |     |

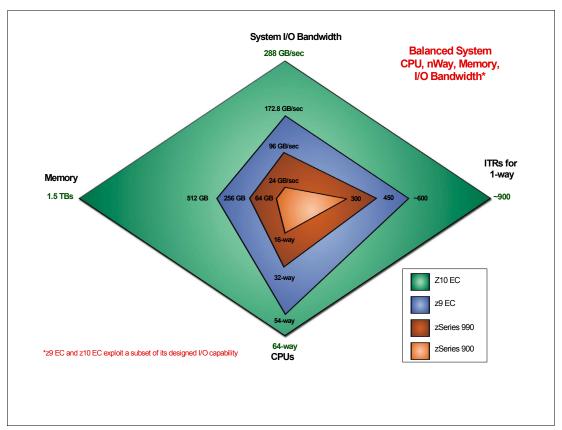

| 3.4 System design numeric comparison       |     |

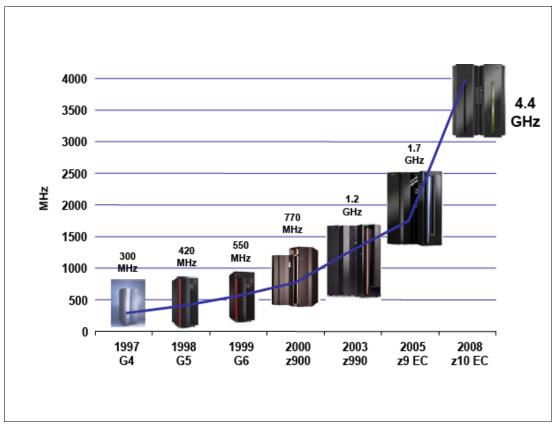

| 3.5 The power of GHz (high frequency)      |     |

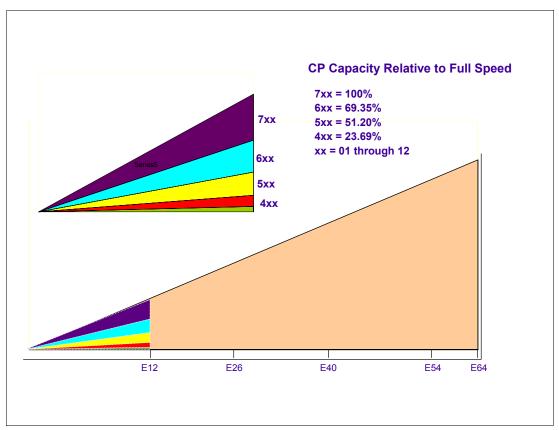

| 3.7 z10 EC hardware model                  |     |

| 3.8 z10 EC sub-capacity models             |     |

| 3.9 z10 EC sub-capacity models.            |     |

| 3.10 Book topology comparison              |     |

| 3.11 NUMA topology                         |     |

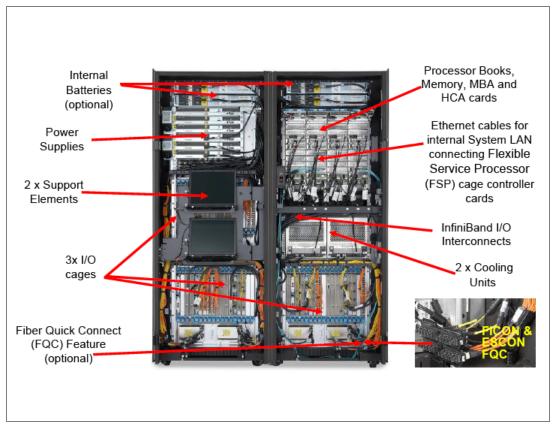

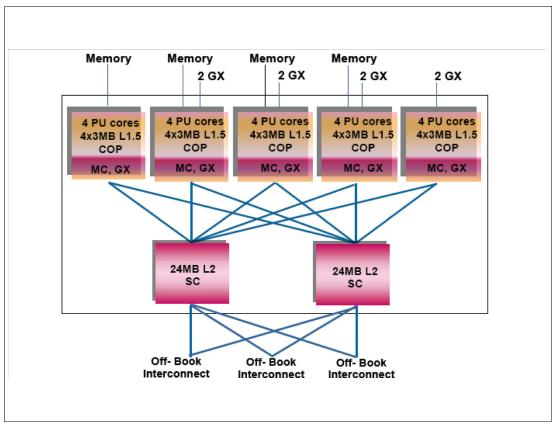

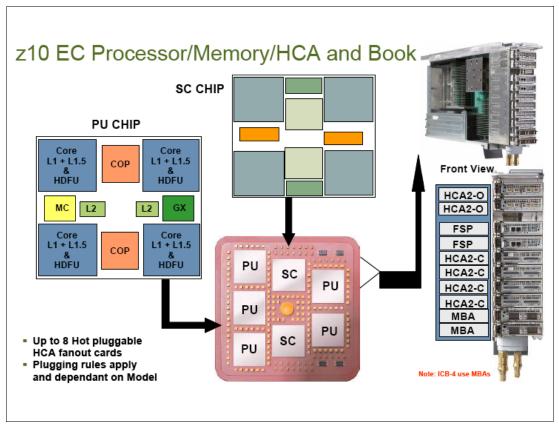

| 3.12 z10 EC Books                          |     |

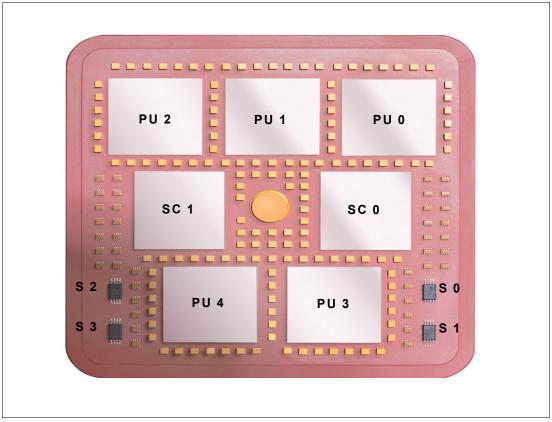

| 3.13 Multi-chip module (MCM)               |     |

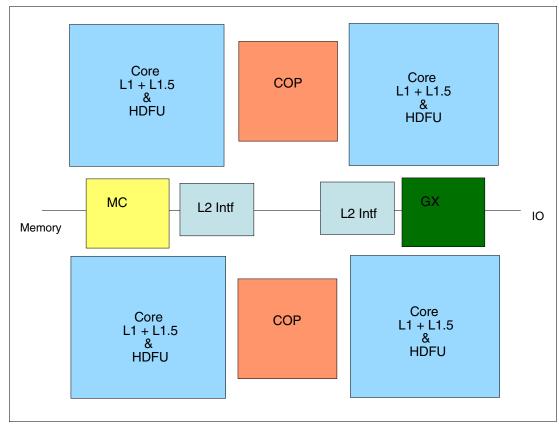

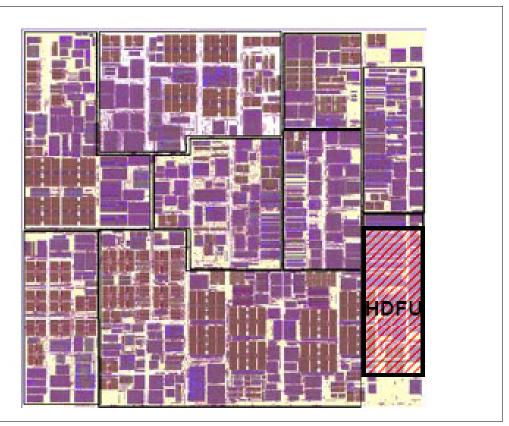

| 3.14 PU chip                               |     |

| 3.15 Book element interconnections         |     |

| 3.16 Pipeline in z10 EC                    |     |

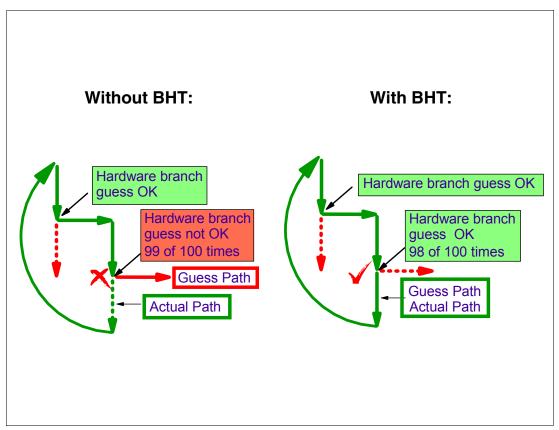

| 3.17 Pipeline branch prediction            |     |

| 3.18 About each z10 EC PU                  |     |

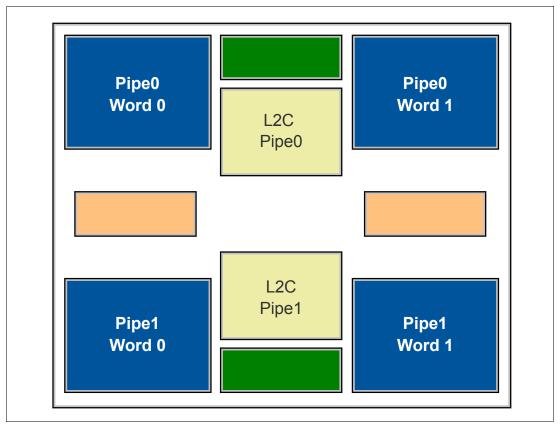

| 3.19 z10 EC storage controller (SC) chip   |     |

| 3.20 Recapping the z10 EC design.          |     |

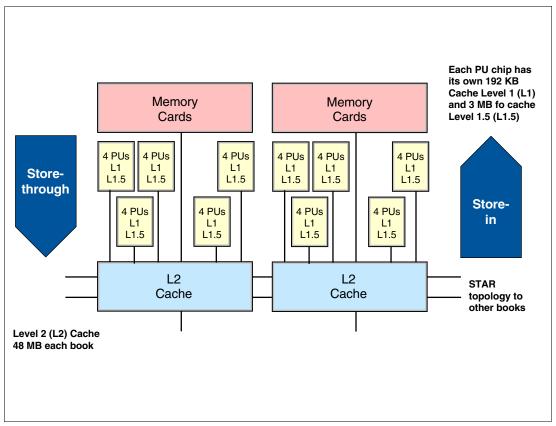

| 3.21 Three levels of cache                 |     |

| 3.22 Software/hardware cache optimization  |     |

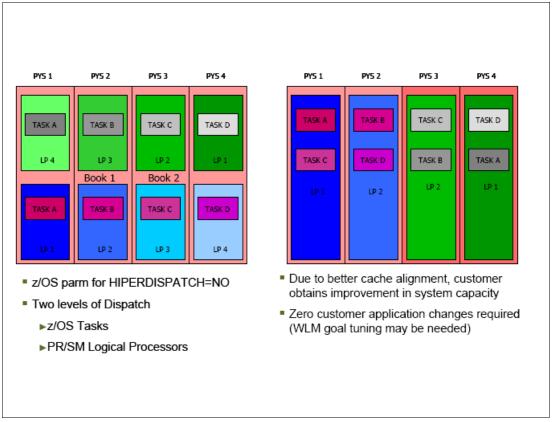

| 3.23 HiperDispatch                         |     |

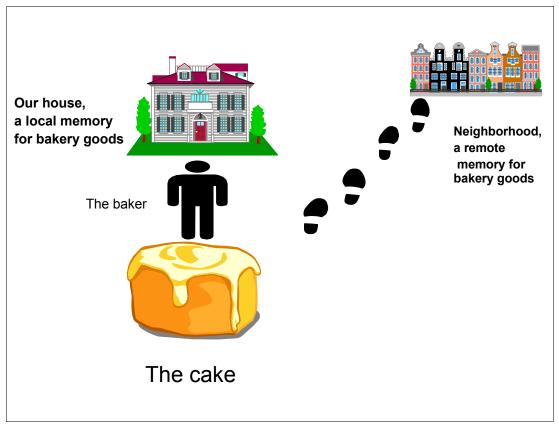

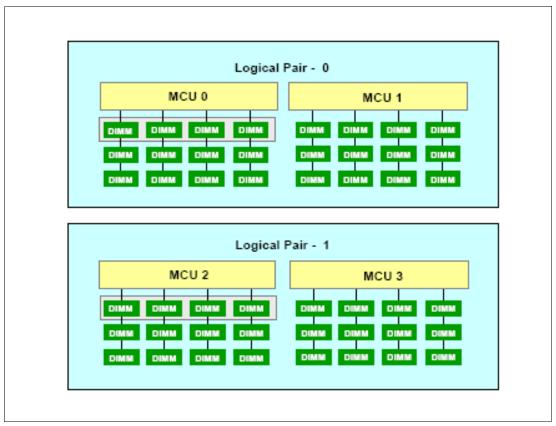

| 3.24 Central storage design                |     |

| 3.25 Addresses and addresses               |     |

| 3.26 Hardware system area (HSA)            |     |

| 3.27 Large page (1 M) support              |     |

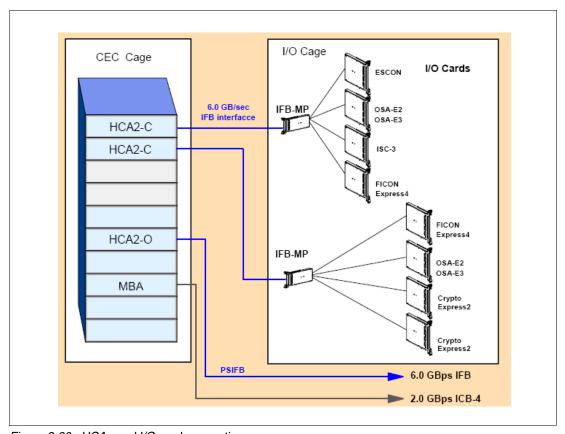

| 3.28 Connecting PU cage with I/O cages     |     |

| 3.29 Detailed connectivity                 |     |

| 3.30 HCA and I/O card connections          | 225 |

| 3.31 InfiniBand interconnect technology    |     |

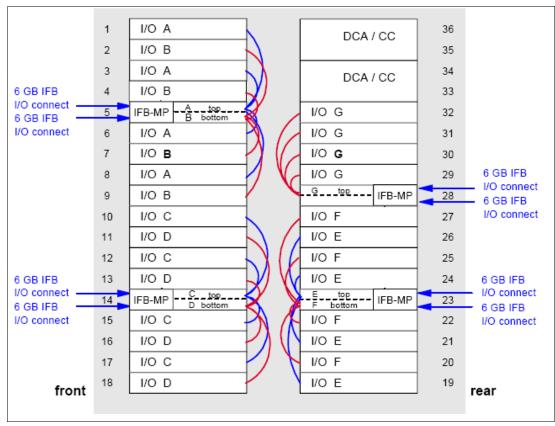

| 3.32 I/O cage                              | 228 |

| 3.33 The I/O data flow                     | 230 |

| 3.34 Redundant I/O Interconnect            | 231 |

| 3.35 z10 EC I/O features supported         | 232 |

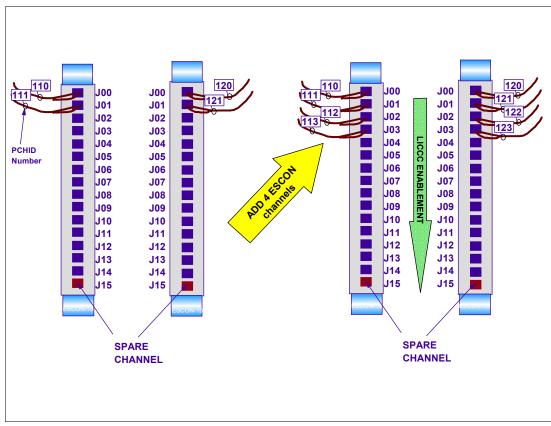

| 3.36 16-port ESCON channel card            | 233 |

| 3.37 FICON features and Extended Distance  | 234 |

| 3.38 Channel subsystem (CSS)               | 236 |

| 3.39 LP ID, MIF ID, and spanning concepts  |     |

| 3.40 Physical channel ID (PCHID)           |     |

| 3.41 Association between CHPIDs and PCHIDs | 242 |

| 3.42 Comparison between System z servers   |     |

| 3.43 IOCP statements example               |     |

| 3.44 Configuration definition process      |     |

| 3.45 Channel availability features         | 248 |

| 3.46 Introduction to MIDAW                                                 |     |

|----------------------------------------------------------------------------|-----|

| 3.47 Channel command word (CCW) concept                                    |     |

| 3.48 CCWs and virtual storage - IDAW Concept                               |     |

| 3.49 DASD extended format                                                  |     |

| 3.50 Using MIDAWs                                                          |     |

| 3.51 Reducing CCWs using MIDAW                                             |     |

| 3.52 MIDAW performance results                                             |     |

| 3.53 Cryptographic hardware features                                       |     |

| 3.54 z10 EC crypto synchronous functions                                   |     |

| 3.55 Crypto Express2                                                       |     |

| 3.56 z10 EC crypto asynchronous functions                                  |     |

| 3.57 Just-in-time capacity upgrades                                        |     |

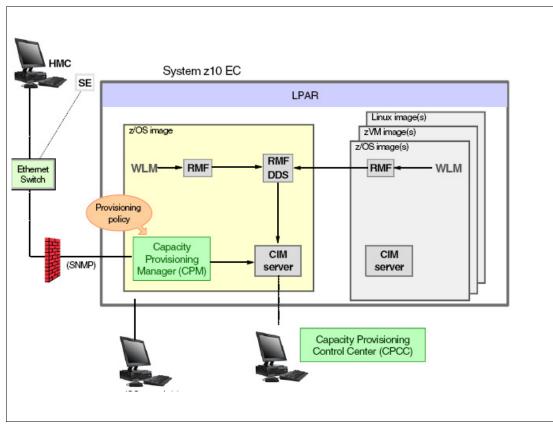

| 3.58 Capacity provisioning                                                 |     |

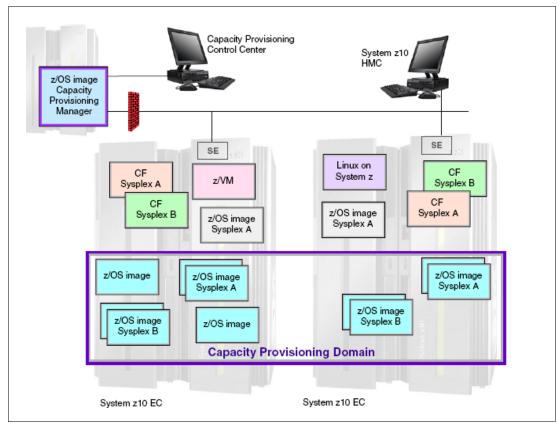

| 3.59 Capacity Provisioning Domain                                          |     |

| 3.60 z10 EC new features                                                   | 276 |

| Chapter 4. System z connectivity                                           | 277 |

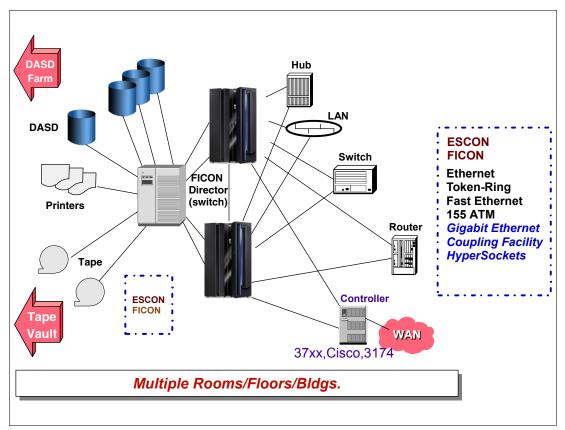

| 4.1 Connectivity overview                                                  |     |

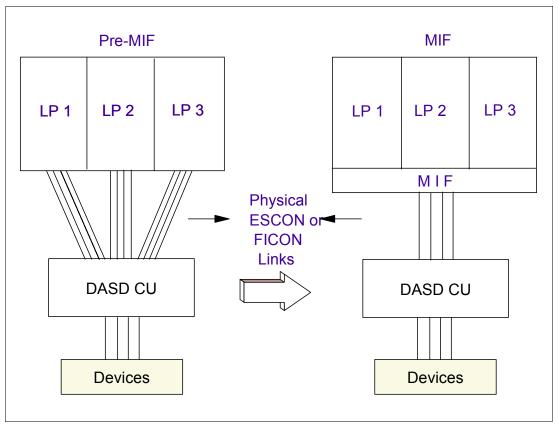

| 4.2 Multiple Image Facility channels                                       |     |

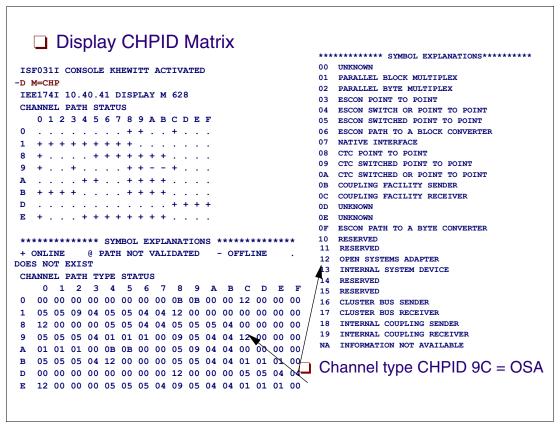

| 4.3 Channel subsystem connectivity                                         |     |

| 4.4 CSS configuration management                                           |     |

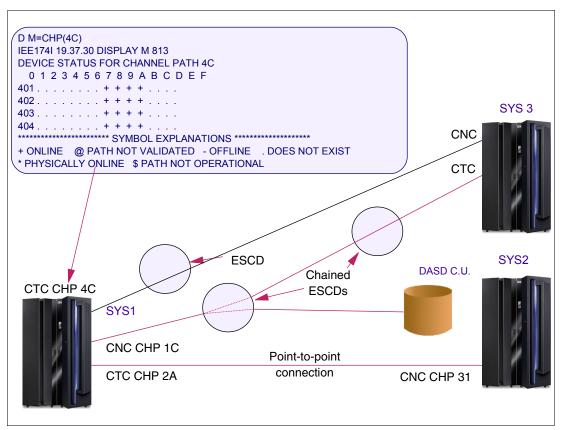

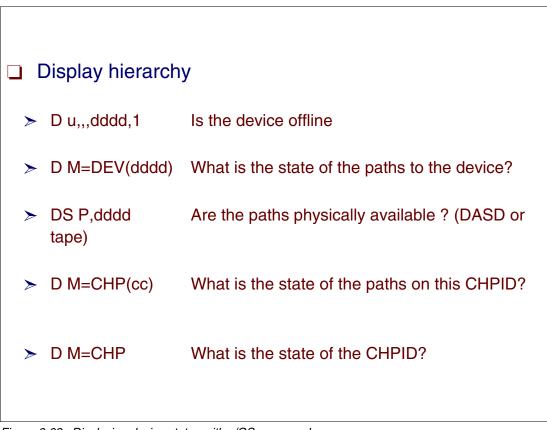

| 4.5 Displaying channel types                                               |     |

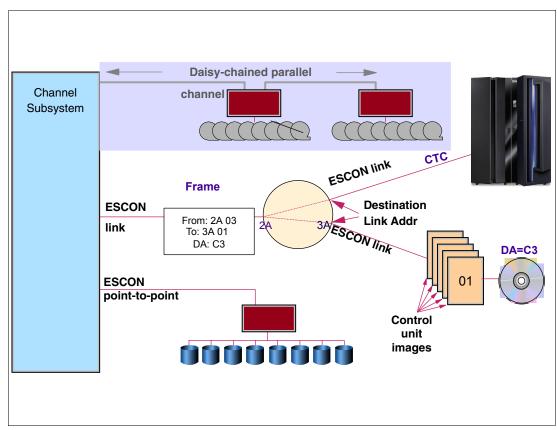

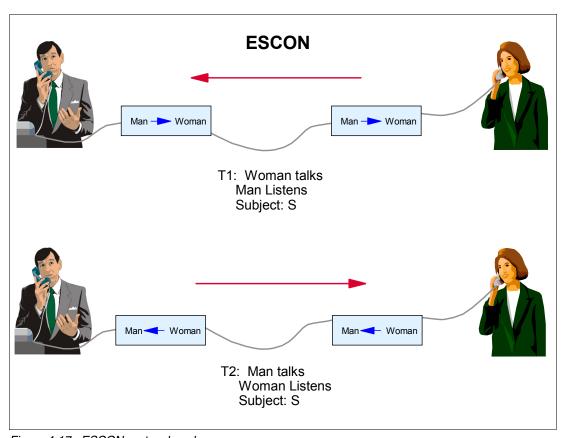

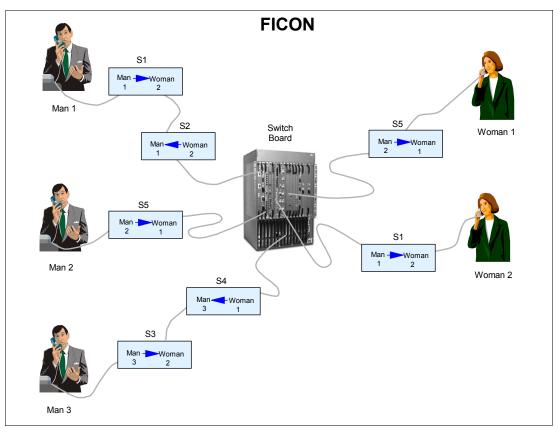

| 4.6 ESCON architecture                                                     |     |

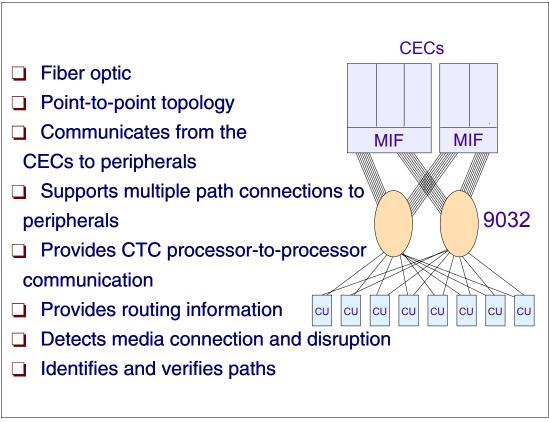

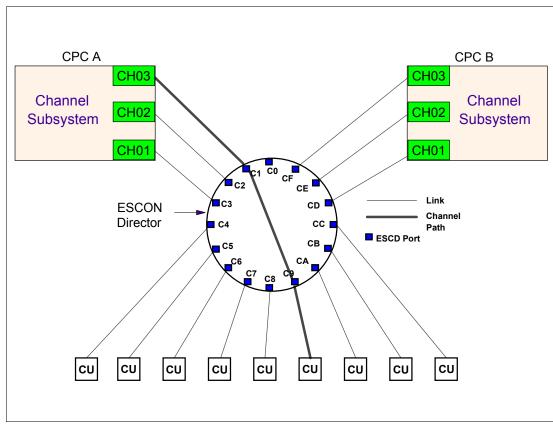

| 4.7 ESCON concepts                                                         |     |

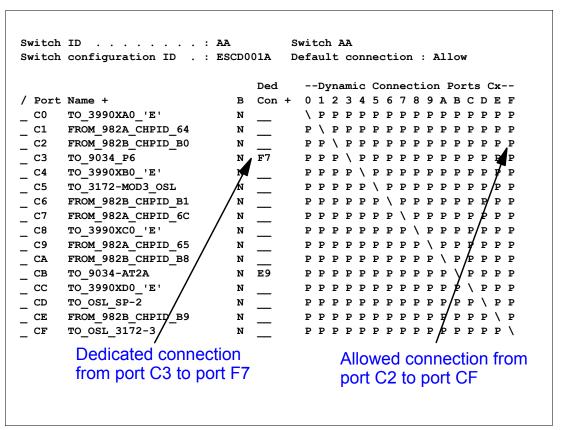

| 4.8 ESCD (switch) functions                                                |     |

| 4.9 ESCON Director (ESCD) description                                      |     |

| 4.10 ESCON Director matrix                                                 |     |

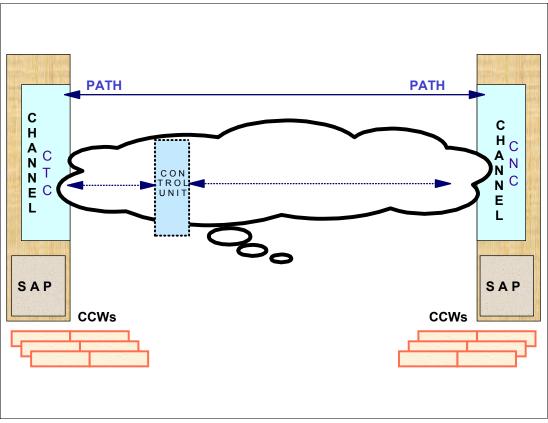

| 4.11 Channel-to-channel adapter                                            |     |

| 4.12 ESCON CTC support                                                     |     |

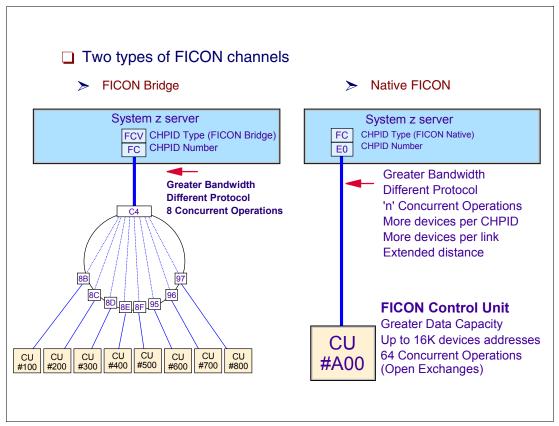

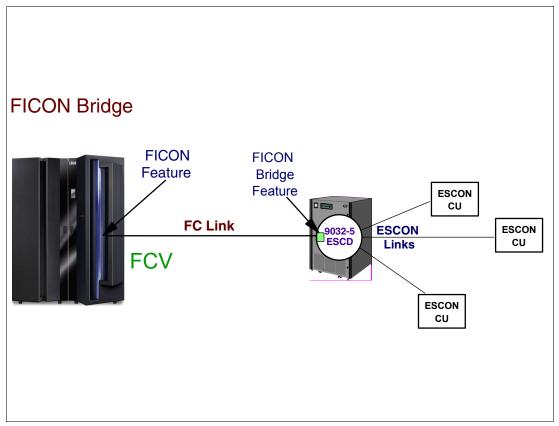

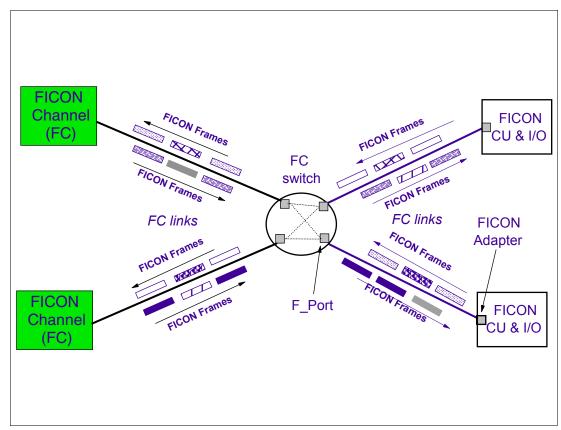

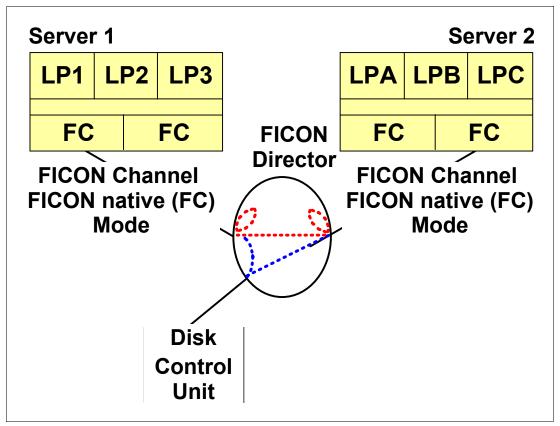

| 4.13 FICON channels                                                        |     |

| 4.14 FICON conversion mode                                                 |     |

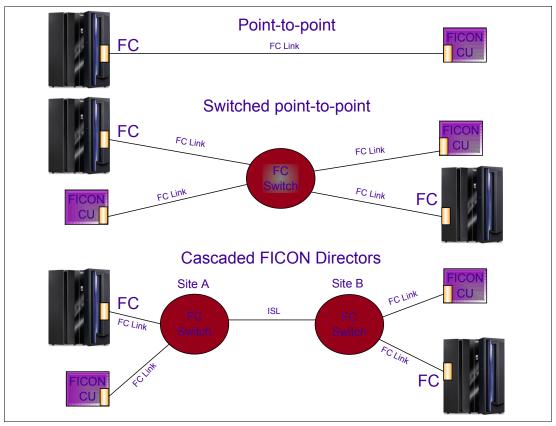

| 4.15 Supported FICON native topologies                                     | 304 |

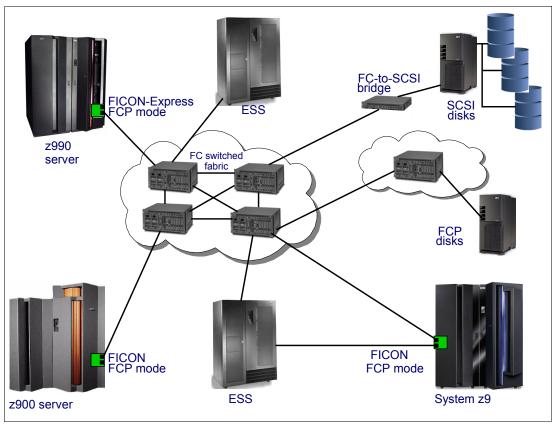

| 4.16 Fibre Channel Protocol (FCP)                                          | 305 |

| 4.17 FICON improvements (1)                                                | 306 |

| 4.18 FICON improvements (2)                                                |     |

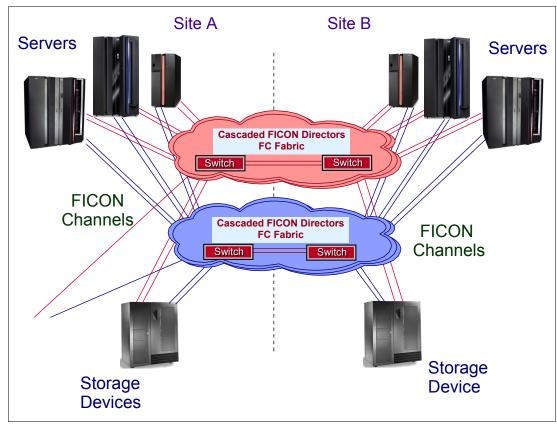

| 4.19 FICON/ESCON numerical comparison                                      | 310 |

| 4.20 FICON switches                                                        | 312 |

| 4.21 Cascaded FICON Directors                                              | 313 |

| 4.22 FICON Channel to Channel Adapter (FCTC)                               | 315 |

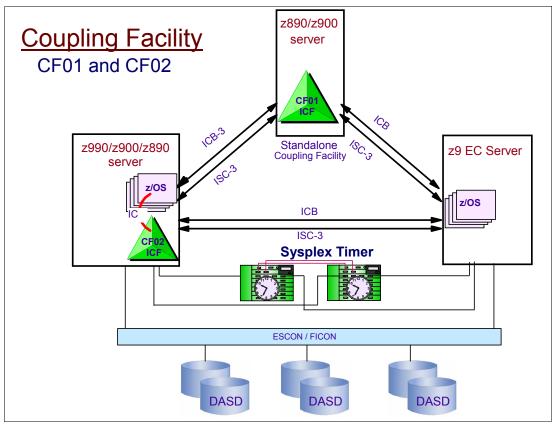

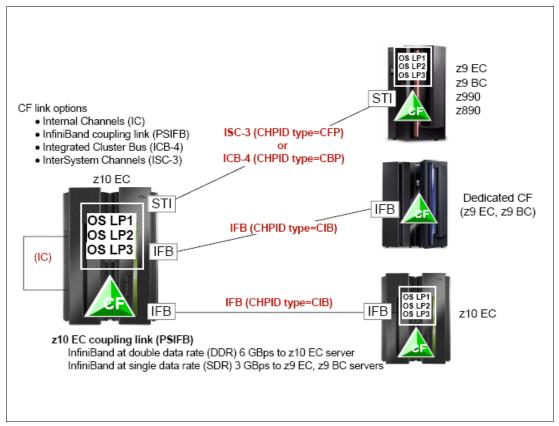

| 4.23 z9 Coupling Facility links                                            | 316 |

| 4.24 z10 EC Coupling Facility connectivity options                         | 318 |

| 4.25 All z10 EC coupling link options                                      | 319 |

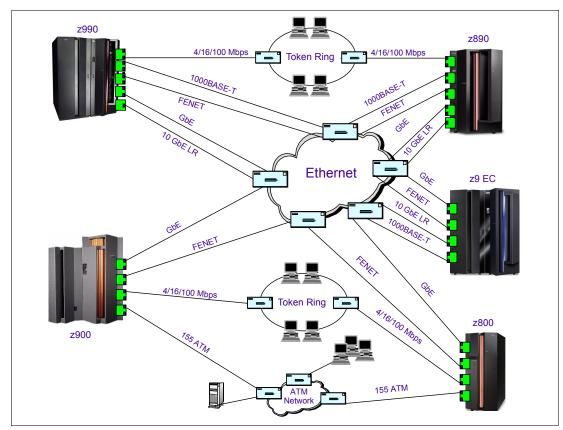

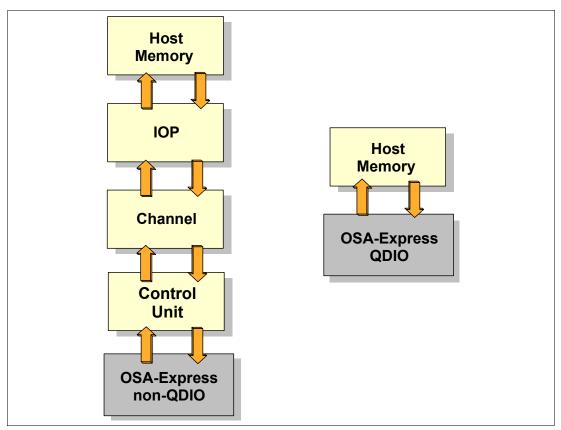

| 4.26 OSA-Express                                                           |     |

| 4.27 QDIO architecture                                                     |     |

| 4.28 HiperSockets connectivity                                             |     |

| 4.29 Hardware Configuration Definition (HCD)                               | 327 |

| Objective 5. Landard months on (LDAD) assessments                          | 000 |

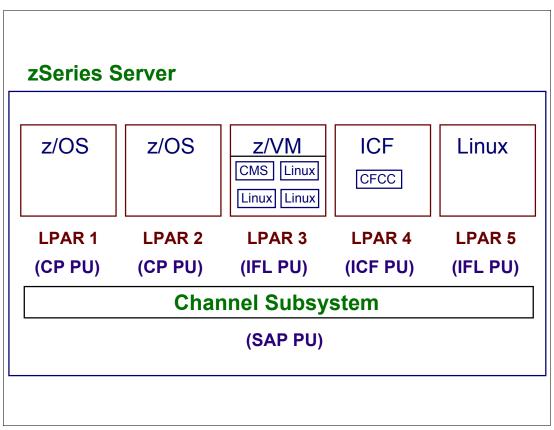

| Chapter 5. Logical partition (LPAR) concepts                               |     |

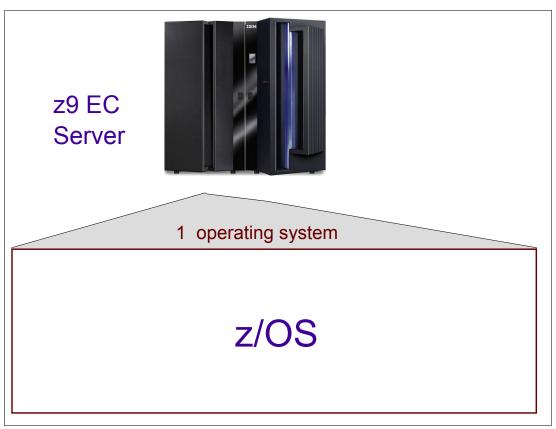

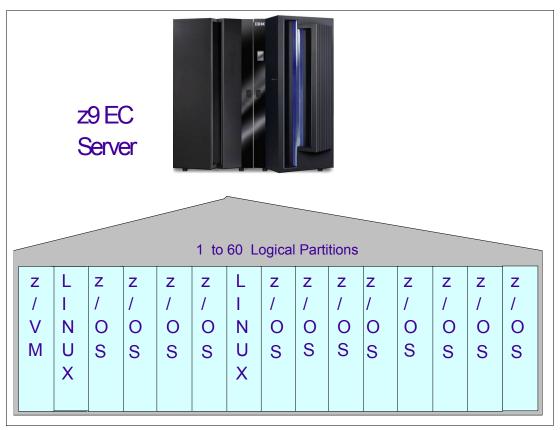

| 5.1 History of operating environments                                      |     |

| <ul><li>5.2 Server in basic mode</li><li>5.3 Server in LPAR mode</li></ul> |     |

|                                                                            |     |

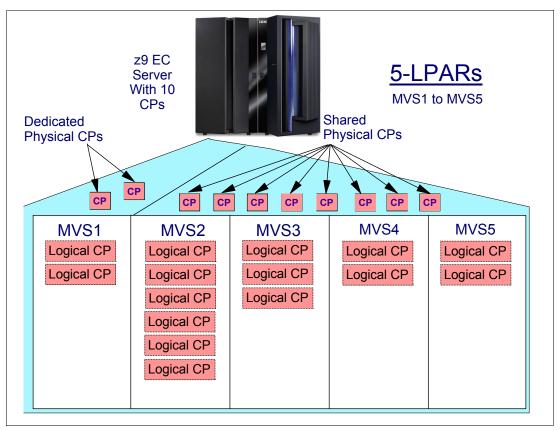

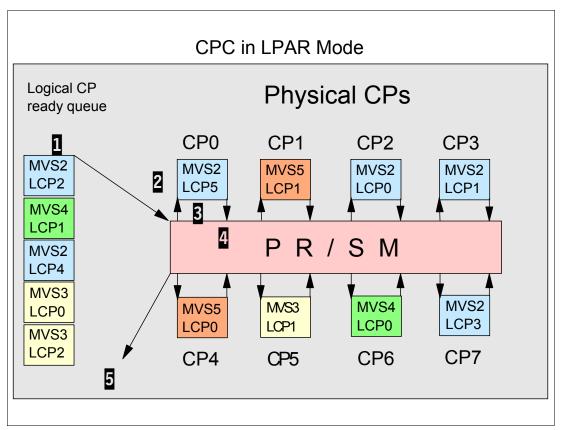

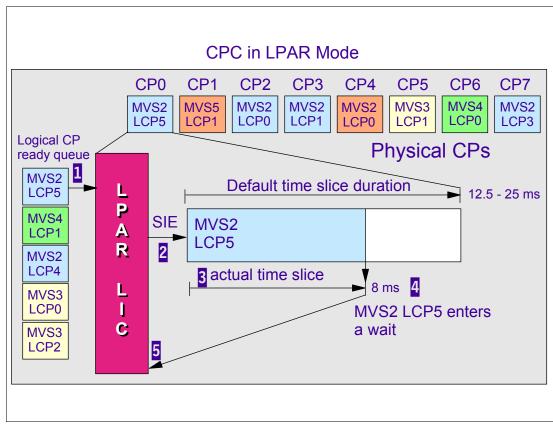

| 5.4 Shared logical CPs example                                             | 335 |

|                                                                            |     |

| 5.6 Reasons for intercepts                         |     |     |

|----------------------------------------------------|-----|-----|

| 5.7 LPAR event-driven dispatching                  |     |     |

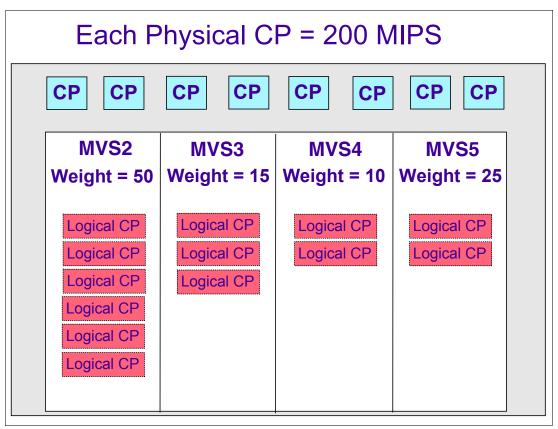

| 5.8 LPAR weights                                   |     |     |

| 5.9 z9 PU pools                                    |     |     |

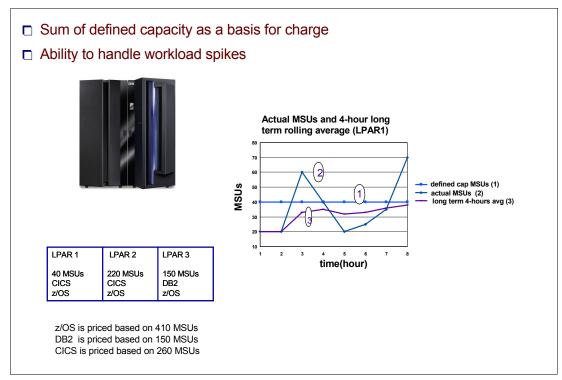

| 5.10 Capping workloads                             |     |     |

| 5.11 LPAR capping                                  |     |     |

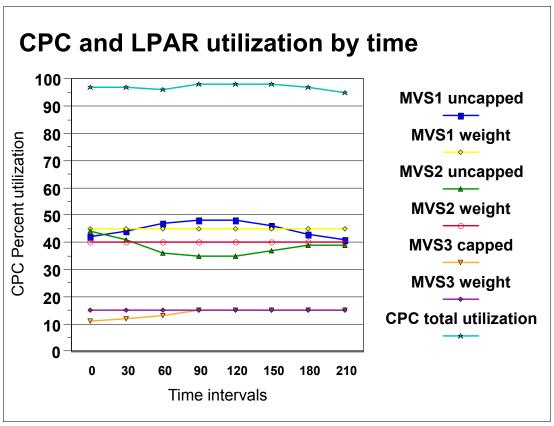

| 5.12 LPAR capped versus uncapped                   |     |     |

| 5.13 Soft capping                                  |     |     |

| 5.14 Group capacity in soft capping                |     |     |

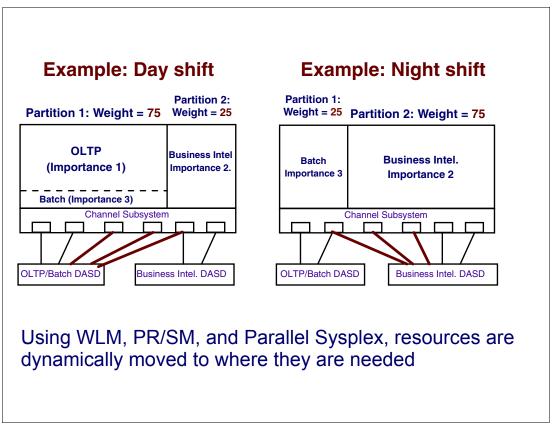

| 5.15 Intelligent Resource Director (IRD)           |     |     |

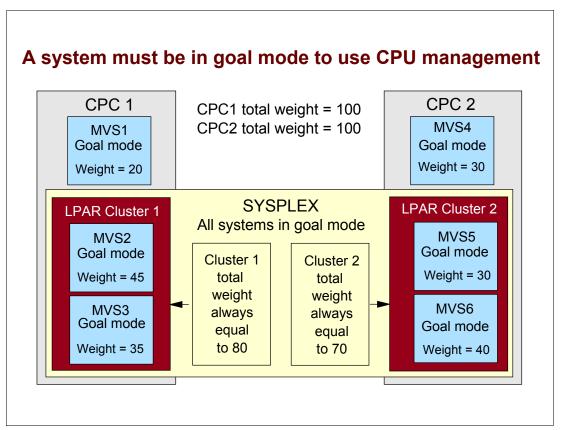

| 5.16 WLM LPAR CPU management                       |     |     |

| 5.17 Workload Manager advantages                   |     |     |

| 5.18 Dynamic Channel Path Management (DCM)         |     |     |

| 5.19 Channel subsystem I/O priority queueing       | • • | 365 |

| Chapter 6. Hardware Configuration Definition (HCD) |     | 369 |

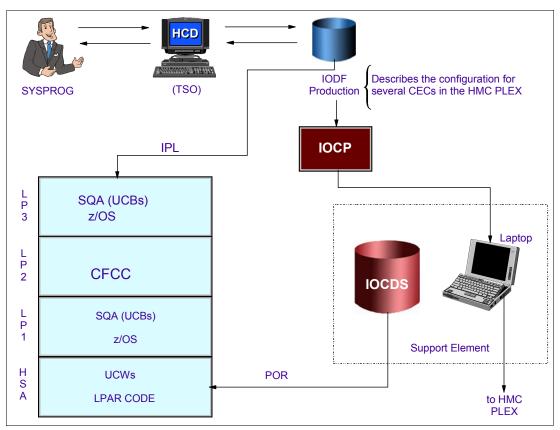

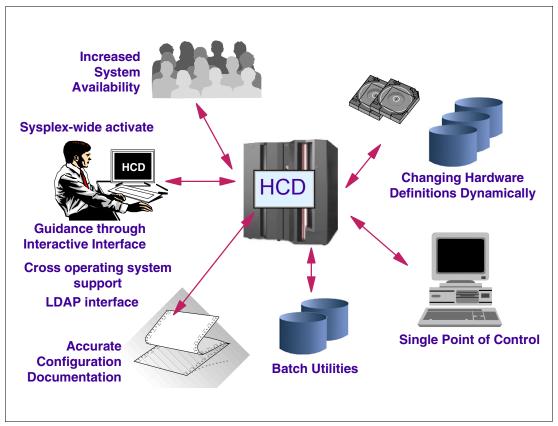

| 6.1 What is HCD                                    |     | 370 |

| 6.2 IOCP example                                   |     | 372 |

| 6.3 IOCP elements                                  |     | 373 |

| 6.4 Hardware and software configuration            |     |     |

| 6.5 HCD functions                                  |     | 377 |

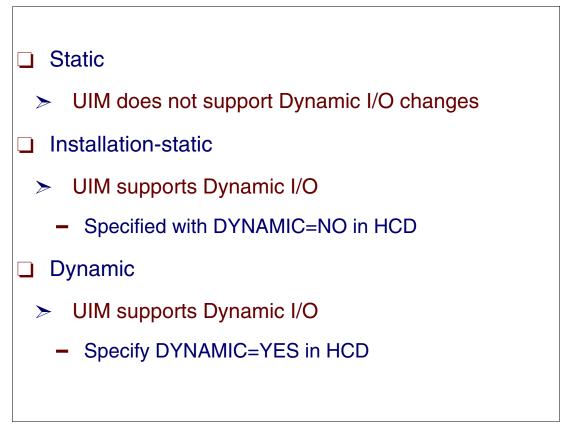

| 6.6 Dynamic I/O reconfiguration                    |     | 379 |

| 6.7 Dynamic I/O reconfiguration device types       |     |     |

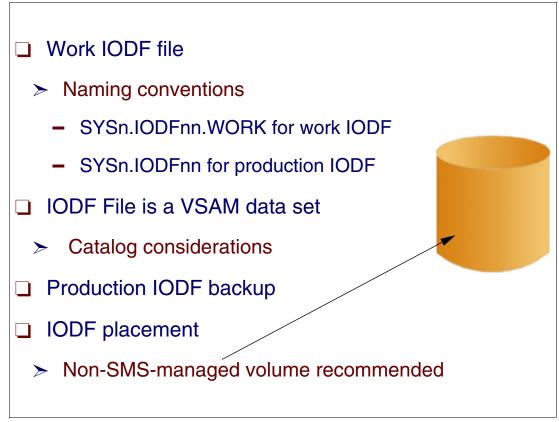

| 6.8 IODF data set                                  |     | 383 |

| 6.9 Definition order                               |     | 386 |

| 6.10 HCD primary menu                              |     | 387 |

| 6.11 Creating a new work IODF                      |     | 388 |

| 6.12 Defining configuration data                   |     | 389 |

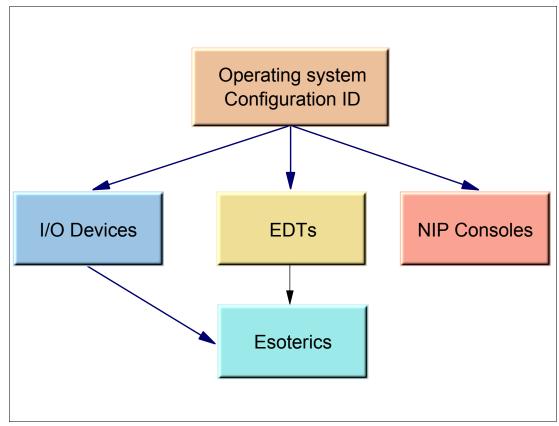

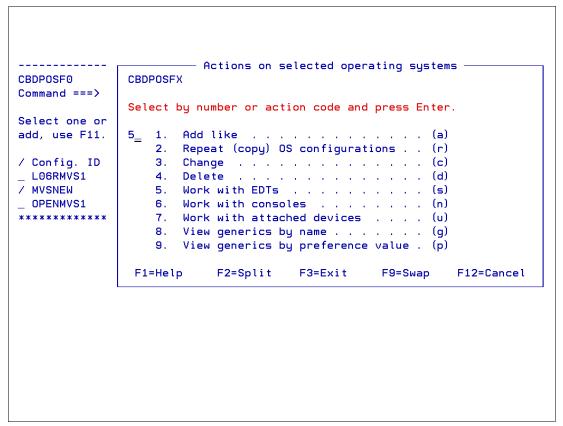

| 6.13 Operating system definition                   |     | 390 |

| 6.14 Defining an operating system                  |     | 391 |

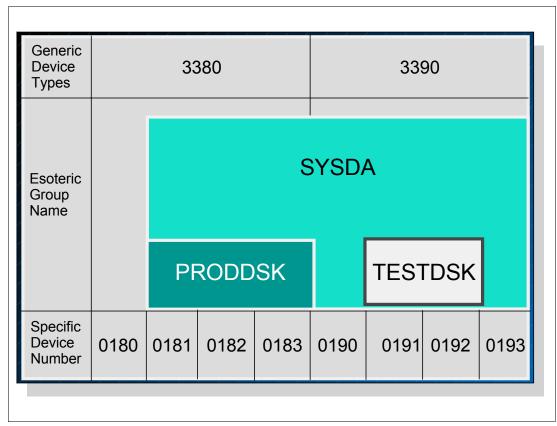

| 6.15 EDT and esoterics                             |     | 392 |

| 6.16 How to define an EDT (1)                      |     | 394 |

| 6.17 How to define an EDT (2)                      |     | 395 |

| 6.18 Defining an EDT identifier                    |     | 396 |

| 6.19 How to add an esoteric                        |     | 397 |

| 6.20 Adding an esoteric                            |     | 399 |

| 6.21 Defining switches                             |     | 400 |

| 6.22 Adding switches                               |     | 402 |

| 6.23 Defining servers                              |     | 403 |

| 6.24 z9 EC server elements                         |     | 405 |

| 6.25 Information for defining a server             |     | 406 |

| 6.26 Defining a server                             |     | 407 |

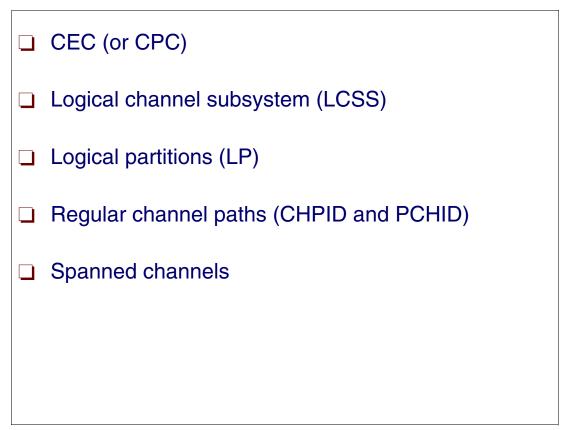

| 6.27 Working with LCSS                             |     | 408 |

| 6.28 Logical channel subsystems defined            |     | 409 |

| 6.29 Adding a logical partition (LP)               |     | 410 |

| 6.30 z9 EC LPAR server configuration               |     |     |

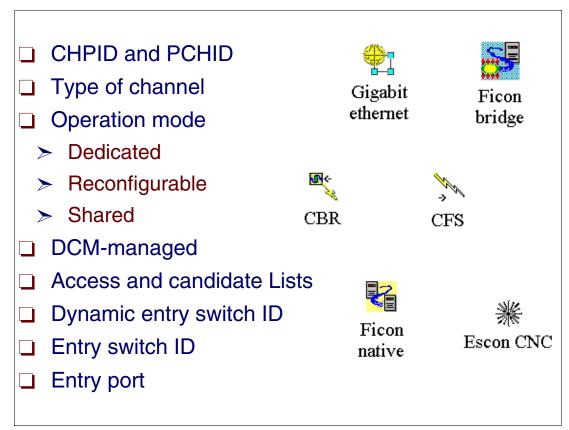

| 6.31 Channel types operation mode                  |     |     |

| 6.32 Channel types                                 |     |     |

| 6.33 Information required to add channels          |     |     |

| 6.34 Working with channel paths                    |     |     |

| 6.35 Adding channel paths dynamically              |     |     |

| 6.36 Adding a channel path                         |     |     |

| 6.37 Defining an access and a candidate list       |     | 420 |

| 6.38 Adding a control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 6.39 Information required to define a control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                  | 23                                                                                                       |

| 6.40 Adding a control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |                                                                                                          |

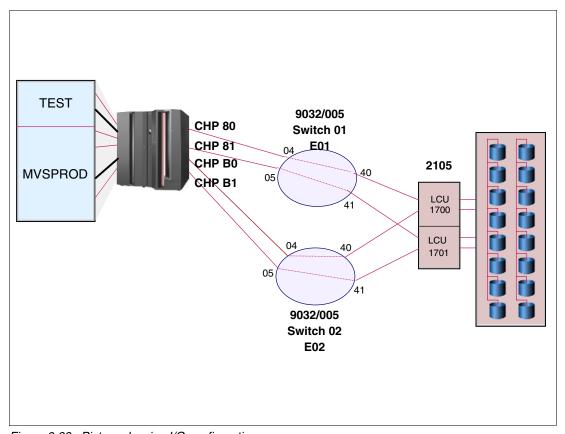

| 6.41 Defining a 2105 control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |                                                                                                          |

| 6.42 Selecting a processor/control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |                                                                                                          |

| 6.43 Servers and channels for connecting control units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |                                                                                                          |

| 6.44 Defining server attachment data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                  |                                                                                                          |

| 6.45 Information required to define a device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |                                                                                                          |

| 6.46 z/OS device numbering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |                                                                                                          |

| 6.47 Defining a device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |                                                                                                          |

| 6.48 Defining device CSS features (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                  |                                                                                                          |

| 6.49 Defining device CSS features (II)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |                                                                                                          |

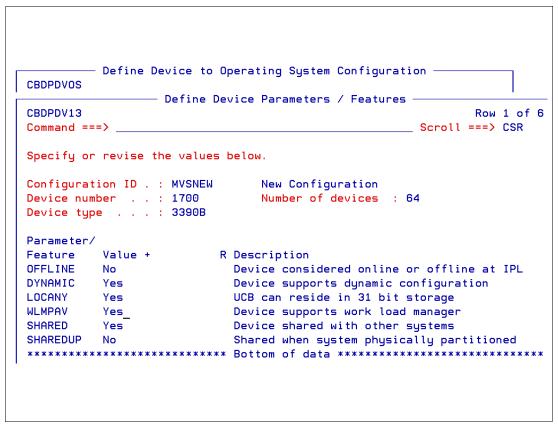

| 6.50 Defining devices to the operating system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                  |                                                                                                          |

| 6.51 Defining operating system device parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |                                                                                                          |

| 6.52 Assigning a device to an esoteric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |                                                                                                          |

| 6.53 Defining an NIP console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |                                                                                                          |

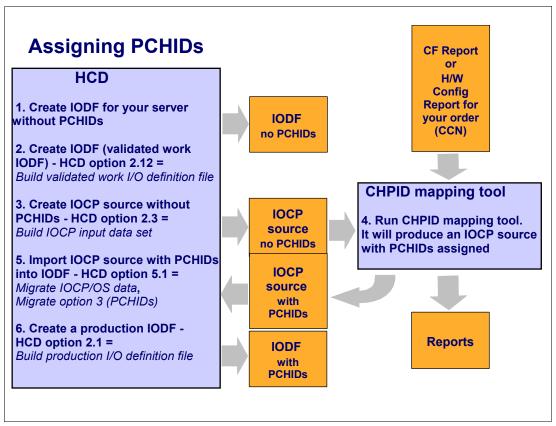

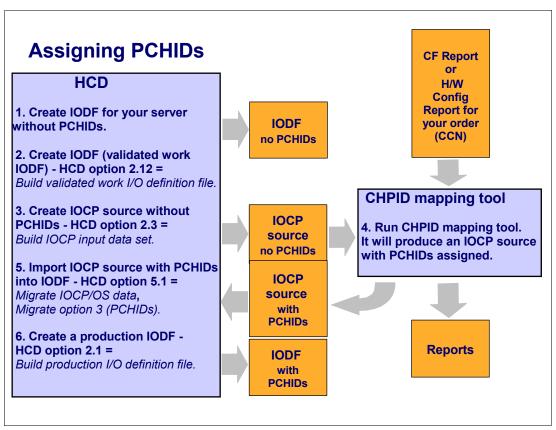

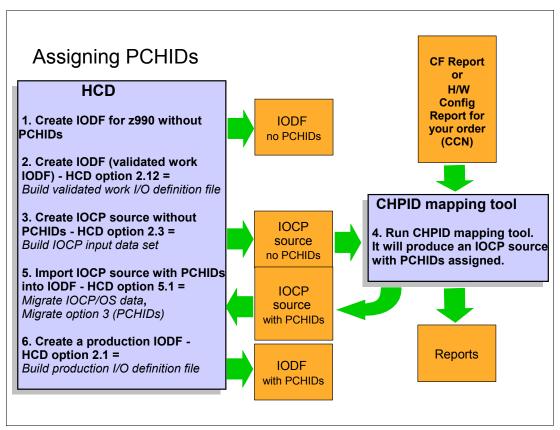

| 6.54 Using the CHPID mapping tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |                                                                                                          |

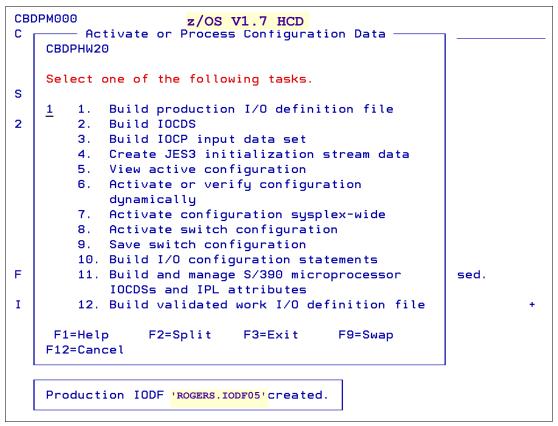

| 6.55 Build a production IODF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |                                                                                                          |

| 6.56 Define the descriptor fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |                                                                                                          |

| 6.57 Production IODF created                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |                                                                                                          |

| 6.58 Activating a configuration with HCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |                                                                                                          |

| 6.59 View an active IODF with HCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |                                                                                                          |

| 6.60 Viewing an active IODF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |                                                                                                          |

| 6.61 Displaying device status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                  |                                                                                                          |

| 6.62 HCD reports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |                                                                                                          |

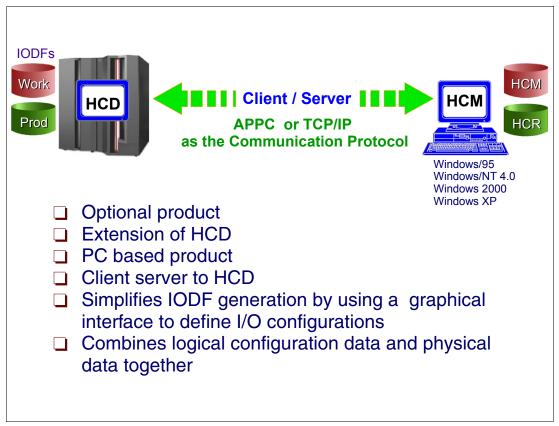

| 6.63 Hardware Configuration Manager (HCM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                | 55                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                  |                                                                                                          |

| Chapter 7. DS8000 series concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                | 57                                                                                                       |

| Chapter 7. DS8000 series concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |                                                                                                          |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                | 58                                                                                                       |

| 7.1 DASD controller capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                | 58<br>60                                                                                                 |

| 7.1 DASD controller capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                               | 58<br>60<br>62                                                                                           |

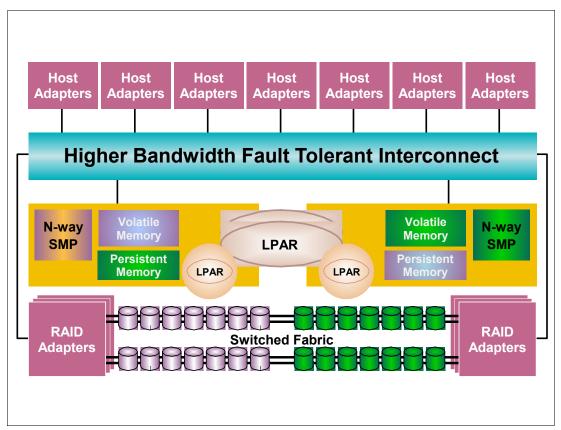

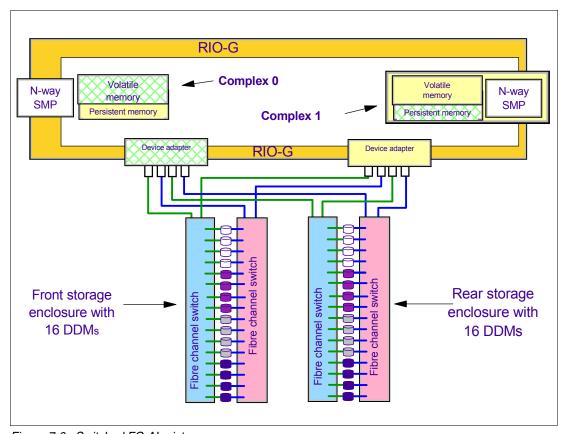

| <ul><li>7.1 DASD controller capabilities</li><li>7.2 DS8000 characteristics</li><li>7.3 DS8000 design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                               | 58<br>60<br>62<br>63                                                                                     |

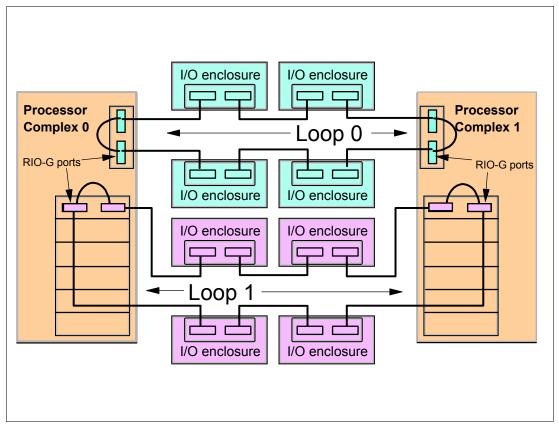

| <ul> <li>7.1 DASD controller capabilities</li> <li>7.2 DS8000 characteristics</li> <li>7.3 DS8000 design</li> <li>7.4 Internal fabric and I/O enclosures</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40                                                               | 58<br>60<br>62<br>63<br>64                                                                               |

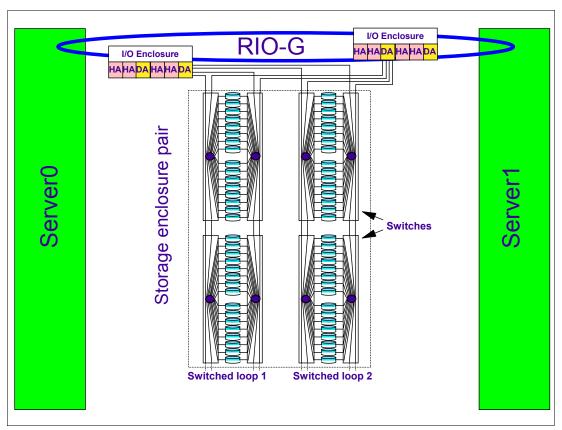

| <ul> <li>7.1 DASD controller capabilities</li> <li>7.2 DS8000 characteristics</li> <li>7.3 DS8000 design</li> <li>7.4 Internal fabric and I/O enclosures</li> <li>7.5 Disk subsystem</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                               | 58<br>60<br>62<br>63<br>64<br>66                                                                         |

| 7.1 DASD controller capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                               | 58<br>60<br>62<br>63<br>64<br>66<br>68                                                                   |

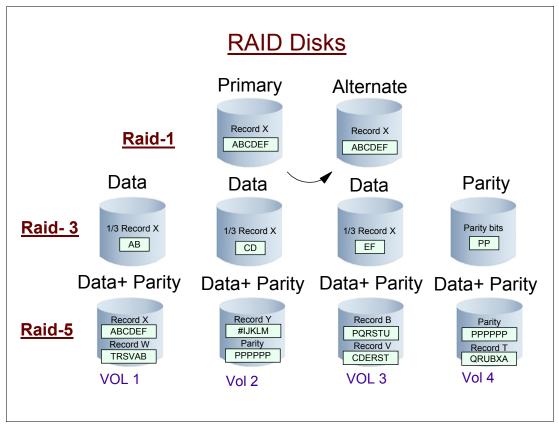

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44                                                               | 58<br>60<br>62<br>63<br>64<br>66<br>68<br>70                                                             |

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4! 4! 4! 4! 4! 4! 4!                                             | 58<br>60<br>62<br>63<br>64<br>66<br>68<br>70<br>72                                                       |

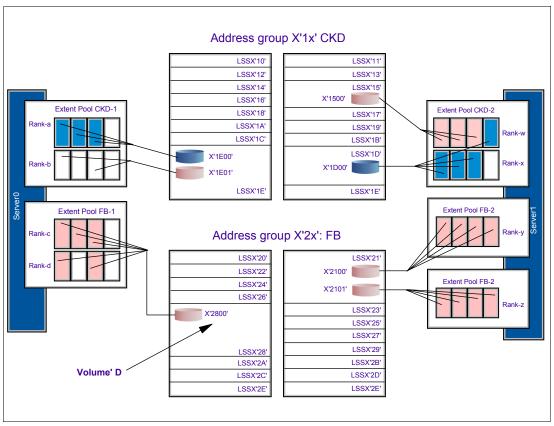

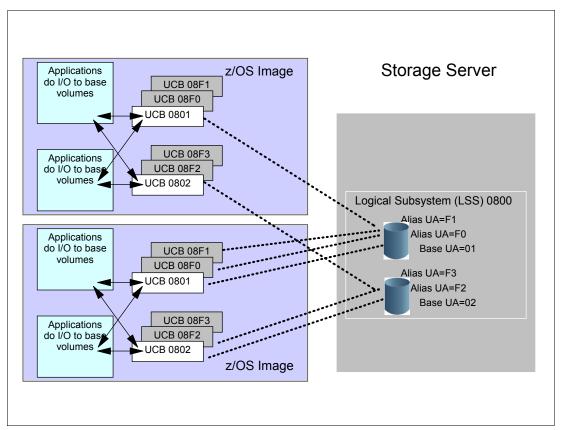

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43<br>44<br>44<br>44<br>44<br>4<br>4                             | 58<br>60<br>62<br>63<br>64<br>66<br>68<br>70<br>72<br>73                                                 |

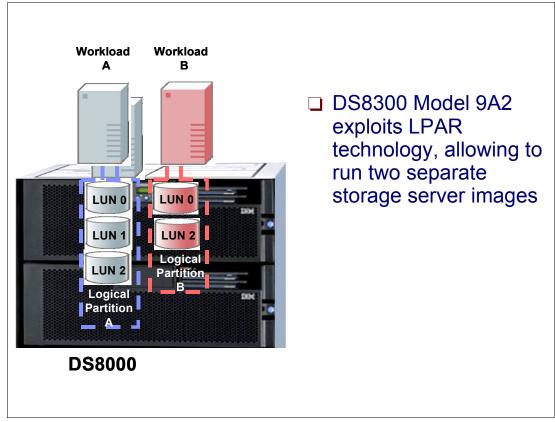

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43<br>40<br>40<br>40<br>40<br>41<br>43<br>43                     | 58<br>60<br>62<br>63<br>64<br>66<br>70<br>72<br>73<br>74                                                 |

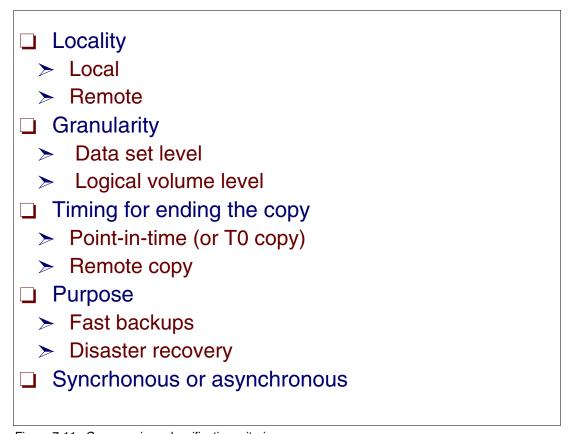

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria                                                                                                                                                                                                                                                                                                                                                                                                                     | 4;<br>40<br>40<br>40<br>41<br>41<br>41<br>41<br>41               | 58<br>60<br>62<br>63<br>64<br>66<br>70<br>72<br>73<br>74                                                 |

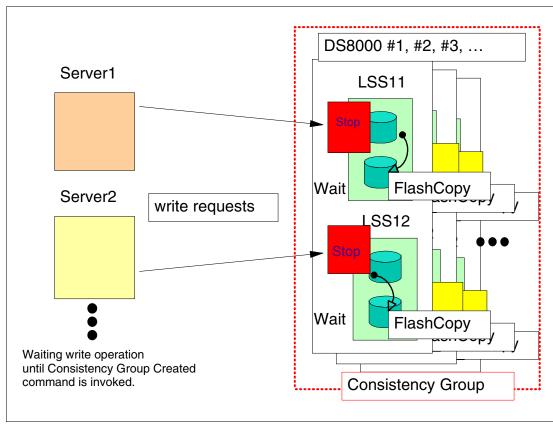

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept                                                                                                                                                                                                                                                                                                                                                                                      | 4! 40 40 40 40 41 42 43 44 44 44 44 44                           | 58<br>60<br>62<br>63<br>64<br>66<br>72<br>73<br>74<br>76<br>78                                           |

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000                                                                                                                                                                                                                                                                                                                                                         | 49<br>40<br>40<br>40<br>41<br>41<br>43<br>44<br>44<br>44<br>44   | 58<br>60<br>62<br>63<br>64<br>66<br>72<br>73<br>74<br>76<br>78                                           |

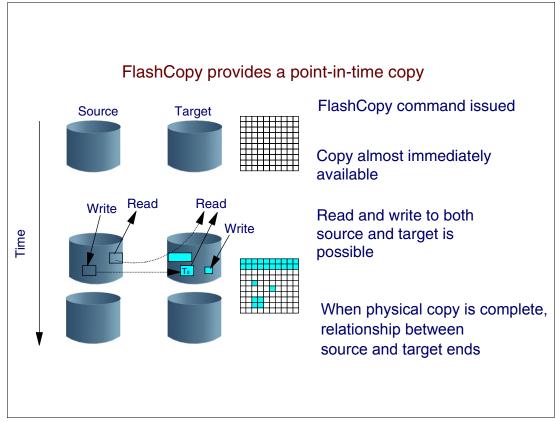

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy                                                                                                                                                                                                                                                                                                                                          | 44<br>46<br>46<br>46<br>4<br>4<br>4                              | 58<br>60<br>62<br>63<br>64<br>66<br>72<br>73<br>74<br>76<br>78                                           |

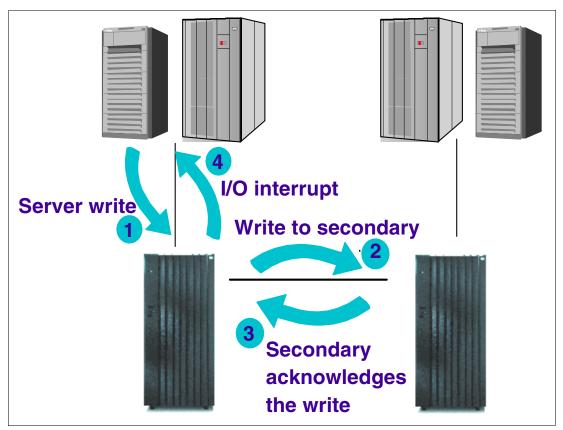

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC) 7.17 Consistency groups in Metro Mirror                                                                                                                                                                                                                  | 44<br>40<br>40<br>40<br>41<br>4<br>4<br>4<br>4<br>4<br>44<br>44  | 58<br>60<br>62<br>63<br>64<br>66<br>70<br>72<br>73<br>74<br>76<br>78<br>82<br>83<br>85                   |

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC)                                                                                                                                                                                                                                                          | 44<br>40<br>40<br>40<br>41<br>4<br>4<br>4<br>4<br>4<br>44<br>44  | 58<br>60<br>62<br>63<br>64<br>66<br>70<br>72<br>73<br>74<br>76<br>78<br>82<br>83<br>85                   |

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC) 7.17 Consistency groups in Metro Mirror                                                                                                                                                                                                                  | 44<br>40<br>40<br>40<br>41<br>4<br>4<br>4<br>4<br>44<br>44<br>44 | 58<br>60<br>62<br>63<br>64<br>66<br>70<br>72<br>73<br>74<br>78<br>79<br>82<br>83<br>85<br>87             |

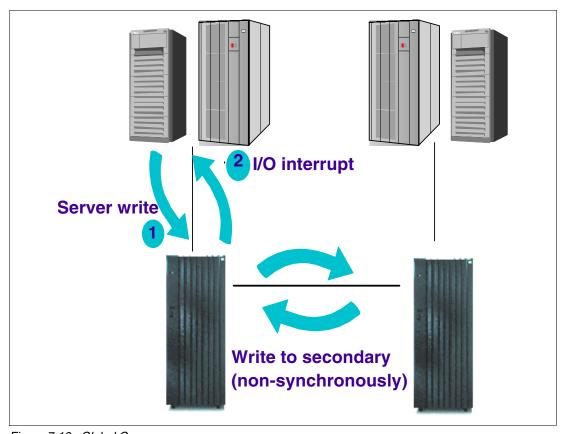

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC) 7.17 Consistency groups in Metro Mirror 7.18 Global Copy (example: PPRC XD)                                                                                                                                                                              | 44 44 44 44 44 44 44 44 44                                       | 58<br>60<br>62<br>63<br>64<br>66<br>72<br>73<br>74<br>76<br>78<br>83<br>85<br>87<br>88                   |

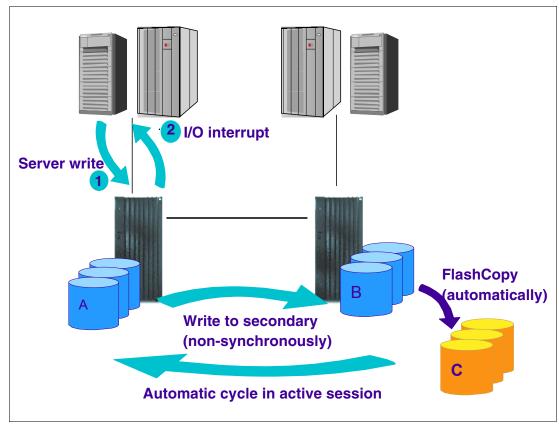

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC) 7.17 Consistency groups in Metro Mirror 7.18 Global Copy (example: PPRC XD) 7.19 Global Mirror (example: async PPRC)                                                                                                                                     | 44 44 44 44 44 44 44 44 44 44 44 44                              | 58<br>60<br>62<br>63<br>64<br>66<br>72<br>73<br>74<br>78<br>78<br>85<br>87<br>88<br>89                   |

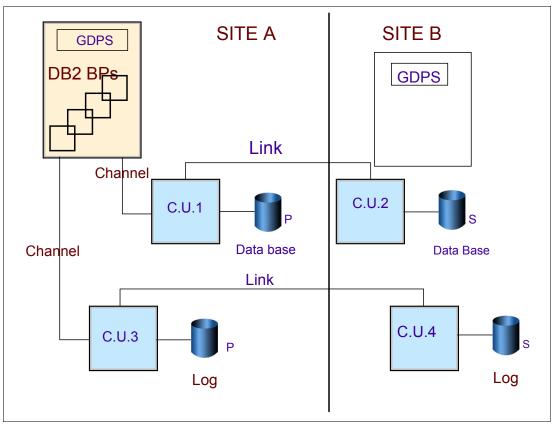

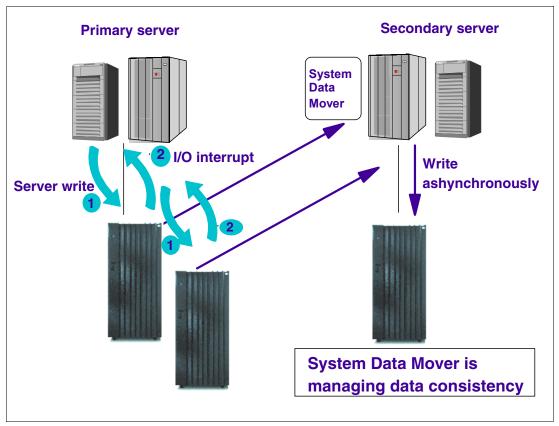

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC) 7.17 Consistency groups in Metro Mirror 7.18 Global Copy (example: April 2 CPRC) 7.19 Global Mirror (example: async PPRC) 7.20 z/OS Global Mirror (example: XRC)                                                                                         | 44 41 41 41 42 43 44 44 44 44 44 44 44 44 44 44                  | 58<br>60<br>62<br>63<br>64<br>66<br>68<br>72<br>73<br>74<br>76<br>82<br>83<br>85<br>87<br>89<br>90       |

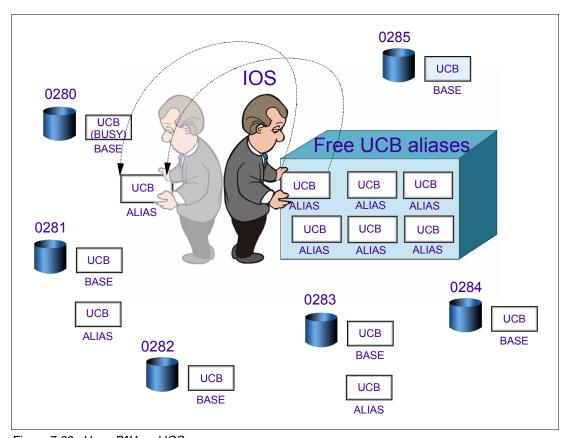

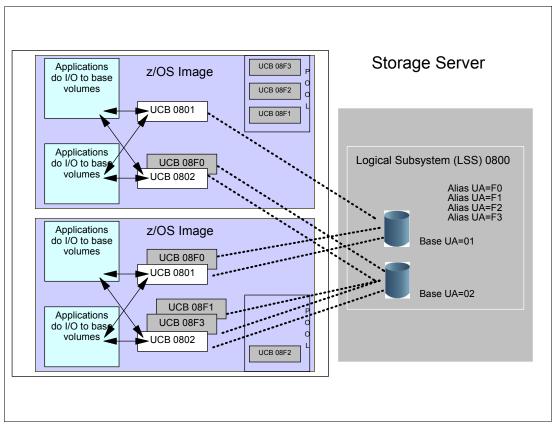

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC) 7.17 Consistency groups in Metro Mirror 7.18 Global Copy (example: Access Volume (PAV) 7.21 Parallel Access Volume (PAV)                                                                                                                                 | 44 44 44 44 44 44 44 44 44 44 44 44 44 44 44 44                  | 58<br>60<br>62<br>63<br>64<br>66<br>70<br>72<br>73<br>74<br>78<br>78<br>82<br>83<br>85<br>88<br>90<br>92 |

| 7.1 DASD controller capabilities 7.2 DS8000 characteristics 7.3 DS8000 design 7.4 Internal fabric and I/O enclosures 7.5 Disk subsystem 7.6 Switched Fibre Channel Arbitrated Loop (FC-AL) 7.7 Redundant array of independent disks (RAID) 7.8 DS8000 types of RAID 7.9 Logical subsystems (LSS) 7.10 Logical partition (LPAR) 7.11 Copy Services classification criteria 7.12 Consistency group concept 7.13 Copy services in DS8000 7.14 FlashCopy 7.15 Consistency group in FlashCopy 7.16 Remote Mirror and Copy (example: PPRC) 7.17 Consistency groups in Metro Mirror 7.18 Global Copy (example: Arconditional PPRC) 7.19 Global Mirror (example: Arconditional PPRC) 7.20 z/OS Global Mirror (example: XRC) 7.21 Parallel Access Volume (PAV) 7.22 HyperPAV feature for DS8000 series | 44 44 44 44 44 44 44 44 44 44 44 44 44 44 44 44 44 44            | 58<br>60<br>62<br>63<br>64<br>66<br>72<br>73<br>74<br>78<br>83<br>85<br>88<br>90<br>92<br>95             |

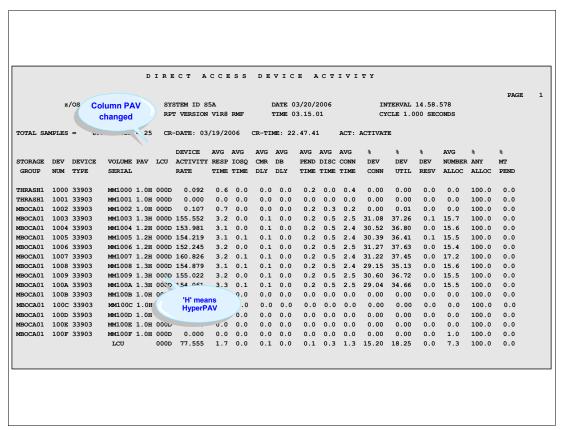

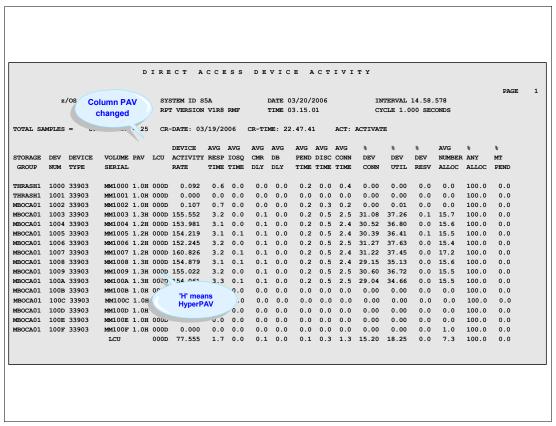

| 7.26 RMF DASD report                             | . 499 |

|--------------------------------------------------|-------|

| 7.27 RMF I/O Queueing report                     |       |

| 7.28 DS8000 Capacity on Demand                   | . 501 |

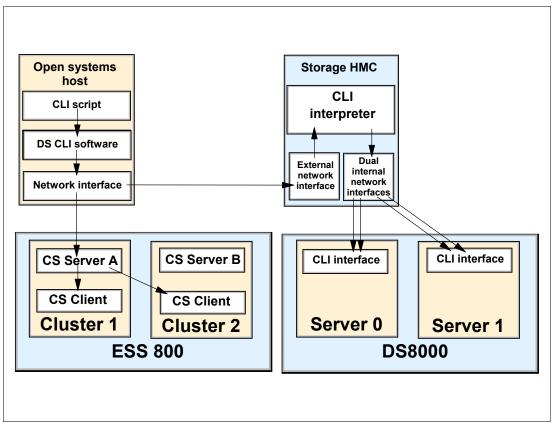

| 7.29 DS command line interface (CLI)             | . 502 |

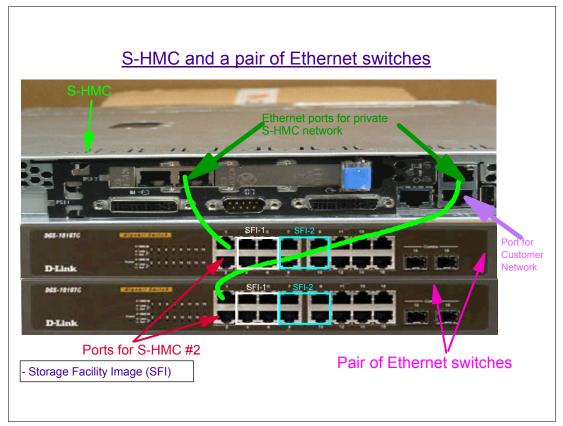

| 7.30 Storage Hardware Management Console (S-HMC) | . 503 |

|                                                  |       |

| Related publications                             | . 505 |

| IBM Redbooks                                     | . 505 |

| Other publications                               | . 505 |

| Online resources                                 | . 505 |

| How to get IBM Redbooks                          | . 506 |

# **Notices**

This information was developed for products and services offered in the U.S.A.

IBM may not offer the products, services, or features discussed in this document in other countries. Consult your local IBM representative for information on the products and services currently available in your area. Any reference to an IBM product, program, or service is not intended to state or imply that only that IBM product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any IBM intellectual property right may be used instead. However, it is the user's responsibility to evaluate and verify the operation of any non-IBM product, program, or service.

IBM may have patents or pending patent applications covering subject matter described in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to:

IBM Director of Licensing, IBM Corporation, North Castle Drive, Armonk, NY 10504-1785 U.S.A.

The following paragraph does not apply to the United Kingdom or any other country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This information could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time without notice.

Any references in this information to non-IBM Web sites are provided for convenience only and do not in any manner serve as an endorsement of those Web sites. The materials at those Web sites are not part of the materials for this IBM product and use of those Web sites is at your own risk.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

Information concerning non-IBM products was obtained from the suppliers of those products, their published announcements or other publicly available sources. IBM has not tested those products and cannot confirm the accuracy of performance, compatibility or any other claims related to non-IBM products. Questions on the capabilities of non-IBM products should be addressed to the suppliers of those products.

This information contains examples of data and reports used in daily business operations. To illustrate them as completely as possible, the examples include the names of individuals, companies, brands, and products. All of these names are fictitious and any similarity to the names and addresses used by an actual business enterprise is entirely coincidental.

#### **COPYRIGHT LICENSE:**

This information contains sample application programs in source language, which illustrate programming techniques on various operating platforms. You may copy, modify, and distribute these sample programs in any form without payment to IBM, for the purposes of developing, using, marketing or distributing application programs conforming to the application programming interface for the operating platform for which the sample programs are written. These examples have not been thoroughly tested under all conditions. IBM, therefore, cannot guarantee or imply reliability, serviceability, or function of these programs.

#### **Trademarks**

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corporation in the United States, other countries, or both. These and other IBM trademarked terms are marked on their first occurrence in this information with the appropriate symbol (® or ™), indicating US registered or common law trademarks owned by IBM at the time this information was published. Such trademarks may also be registered or common law trademarks in other countries. A current list of IBM trademarks is available on the Web at http://www.ibm.com/legal/copytrade.shtml

The following terms are trademarks of the International Business Machines Corporation in the United States, other countries, or both:

PR/SM™

**RACF®**

RMF™

S/360<sup>TM</sup>

S/370TM

S/390®

Seascape®

System z™

System z10™

System/360™

System/370™

TotalStorage®

WebSphere® 3090™

VSE/ESA™

**VTAM®**

System Storage™

System z9®

Sysplex Timer®

Redbooks®

Resource Link™

Redbooks (logo) @® ES/9000® e-business on demand® **ESCON®** pSeries® FlashCopy® z/Architecture® **FICON®** z/OS® Geographically Dispersed Parallel Sysplex<sup>TM</sup> z/VM® **GDPS®** z/VSETM HiperSockets™ zSeries® z10™ HyperSwap™ z10 EC™ **IBM®** z9<sup>TM</sup> IMS™ Common User Access® Language Environment® **CICS®** MQSeries® **MVSTM CUA®** DB2® MVS/ESA™ DFSMS™ MVS/XATM DS6000™ Parallel Sysplex® DS8000™ Power PC®

PowerPC®

POWER5™

Manager™

The following terms are trademarks of other companies:

Enterprise Storage Server®

Architecture/370™

Enterprise Systems

ECKD™

SAP R/3, SAP, and SAP logos are trademarks or registered trademarks of SAP AG in Germany and in several other countries.

InfiniBand Trade Association, InfiniBand, and the InfiniBand design marks are trademarks and/or service marks of the InfiniBand Trade Association.

Processor Resource/Systems

Java, JVM, RSM, Sun, and all Java-based trademarks are trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

Microsoft, Windows, and the Windows logo are trademarks of Microsoft Corporation in the United States, other countries, or both.