# Professional Radio GP Series

Power Distribution and Controller Service Information

Issue: June 2002

## **Computer Software Copyrights**

The Motorola products described in this manual may include copyrighted Motorola computer programs stored in semiconductor memories or other media. Laws in the United States and other countries preserve for Motorola certain exclusive rights for copyrighted computer programs, including the exclusive right to copy or reproduce in any form, the copyrighted computer program. Accordingly, any copyrighted Motorola computer programs contained in the Motorola products described in this manual may not be copied or reproduced in any manner without the express written permission of Motorola. Furthermore, the purchase of Motorola products shall not be deemed to grant, either directly or by implication, estoppel or otherwise, any license under the copyrights, patents or patent applications of Motorola, except for the normal non-exclusive royalty-free license to use that arises by operation of law in the sale of a product.

# **Table of Contents**

# **Chapter 1 THEORY OF OPERATION**

| 1.0   | Overview                                                        | 1-1  |

|-------|-----------------------------------------------------------------|------|

| 2.0   | Radio Power Distribution                                        | 1-1  |

| 3.0   | Controller Circuits                                             | 1-2  |

| 3     | B.1 Controller Architecture                                     | 1-2  |

| 3     | 3.2 MCU Digital Architecture                                    | 1-2  |

| 3     | 3.3 Real Time Clock                                             | 1-3  |

| 3     | 3.4 ModB/Vstby Supply                                           | 1-4  |

| 3     | 3.5 Audio/Signaling Architecture                                | 1-4  |

| Chapt | er 2 TROUBLESHOOTING CHARTS                                     |      |

|       | UHF/ UHF2/ 300R1 Controller                                     |      |

|       | VHF Controller                                                  |      |

| 3.0   | Lowband Controller                                              | 2-3  |

| Chapt | er 3 CONTROLLER SCHEMATICS                                      |      |

|       | Allocation of Schematics and Circuit Boards                     | 3-1  |

| 2.0   | Controller - Set 1 (PCB 8480450Z03, 8485641Z02, 8486062B12/B14, |      |

|       | 8480587Z01, 8485677Z01, 8485726Z01, 8480641Z03)                 |      |

| 3.0   | Controller - Set 2 (PCB 8486101B09/B10)                         |      |

| 4.0   | Controller - Set 3 (PCB 8485658Z01)                             |      |

| 5.0   | Controller - Set 4 (PCB 8486062B16)                             |      |

| 6.0   | Controller - Set 5 (PCB 8480450Z13/14, 8485641Z06, 8485726Z04)  | 3-27 |

### THEORY OF OPERATION

#### 1.0 Overview

This Chapter provides a detailed theory of operation for the power distribution and controller circuits in the radio. The components for these circuits are contained on the Main Board. Refer to the RF sections of this manual for the component location details and the parts lists for these circuits.

#### 2.0 Radio Power Distribution

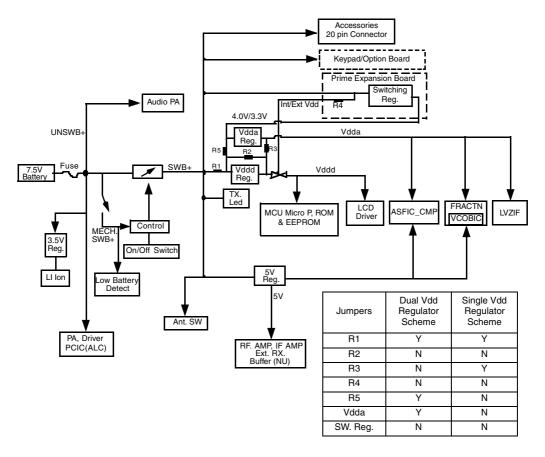

Figure 1-1: DC Power Distribution Block Diagram

Figure 1-1 illustrates the DC distribution throughout the radio board. A 7.5V battery (BATT 7.5V) supplies power directly to the electronic on/off control as UNSWB+. When the radio is turned on, MECH\_SWB+ (on/off/volume control) will trigger the electronic on/off control (momentary-on path), then SWB+ is distributed as shown in Figure1-1. Vdda from 3.3V Vdda regulator will then supply the microprocessor. Data is then sent to ASFIC\_CMP to turn on GCB4(DAC). GCB4 will take over the momentary-on path within 12ms. SWB+ will continue to support the whole board until the radio is turned off.

Radio will be turned-off on two conditions;

- 1. MECH\_SWB+ turned off

- 2. Low battery

When low battery level is detected by the microprocessor through both conditions above, it will store the radio personality data to EEPROM before turning off.

1-2 THEORY OF OPERATION

#### 3.0 Controller Circuits

#### 3.1 Controller Architecture

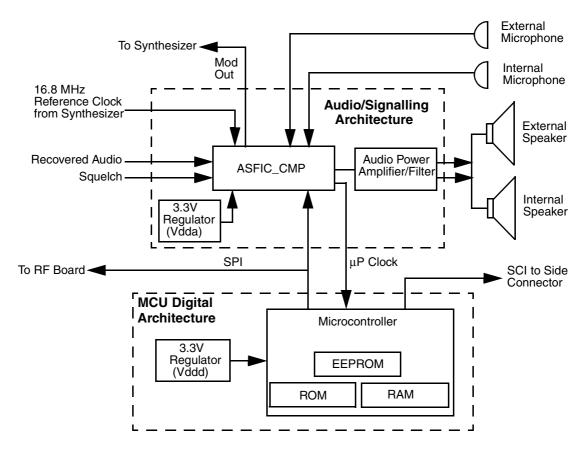

The controller board is the central interface between the various subsystems of the radio. It is separated into MCU digital and audio/signalling architectures as shown in Figure 1-2.

Figure 1-2 Controller Block Diagram

#### 3.2 MCU Digital Architecture

(Refer to Figure 1-2, the Microprocessor and the Memory schematic diagrams)

The digital architecture portion consists of a microcontroller and associated EEPROM, RAM, and ROM memories. The architecture is commonly used for both low-tier and high-tier products and also includes conventional and trunking portables. Combinations of different size RAM and ROM are available to support various application software. RAM supports 8KB and 32KB sizes. ROM supports 128KB, 256KB, and 512KB sizes. Table 1-1 shows the ROM, RAM and EEPROM requirements for different applications.

Controller Circuits 1-3

| RADIO               |              | ROM (KB) | EXT RAM<br>(KB) | EEPROM<br>(KB) |

|---------------------|--------------|----------|-----------------|----------------|

| Conventional MDC    | GP140        | 128K     | -               | 8K             |

| Conventional 5 Tone | GP320, GP340 | 512K     | 16K             | 16K            |

| Conventional 5 Tone | GP360, GP380 | 512K     | 16K             | 16K            |

| Private Plus        | GP240, GP280 | 512K     | 16K             | 16K            |

| SmartZone           | GP540, GP580 | 512K     | 16K             | 16K            |

| MPT                 | GP640, GP680 | 512K     | 16K             | 16K            |

| MPT                 | GP1280       | 512K     | 16K             | 16K            |

Table 1-1 Radio Memory Requirements

#### 3.3 Real Time Clock

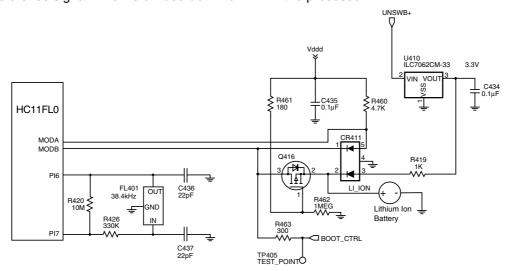

(Refer to Figure 1-3 and the Microprocessor schematic diagram)

Radios with displays support a Real Time Clock (RTC) module for purposes of message time stamping and time keeping. The RTC module resides in the microcontroller. The clock uses a back-up Lithium Ion battery for operating power when the primary battery is removed.

#### 3.3.1 Circuit Description

The RTC module circuit, shown in Figure 1-3, is powered by the ModB/Vstby pin and PI6/PI7 from the crystal oscillator circuit. A clock frequency of 38.4kHz from a crystal oscillator provides the reference signal which is divided down to 1 Hz in the processor.

Figure 1-3 RTC Circuit

As the RTC module is powered separately from the processor Vdd, the RTC is kept active through the ModB / Vstby pin which provides the Lithium battery back-up power when the radio is switched off.

1-4 THEORY OF OPERATION

A MOSFET Q416 switches in the LiO supply when Vdd is removed. Q416 also provides isolation from BOOT\_CTRL function in the event of radio program flashing. The 3.3V regulator charges the Lithium battery.

#### 3.4 ModB/Vstby Supply

The supply to the ModB/Vstby pin varies depending on the conditions listed in Table 1-2.

Condition **Circuit Operation** Radio On Vdd supply voltage via CR411 Radio Off • Vdd turned off • Q416 gate pulled low by R462 • Q416 switched on • U410 supplies 3.2V to ModB/Vstby Primary battery removed · Vdd turned off Q416 gate pulled low by R462 • Q416 switched on • Lithium battery provides 3.2V to ModB/Vstby Flash Mode • Boot\_Ctrl line pulled low • ModA & ModB go low • Processor in boot-strap mode

Table 1-2 ModB/Vstby Supply Modes

#### 3.5 Audio/Signaling Architecture

(Refer to Figure 1-2 and the ASFIC/ON\_OFF and Audio Power Amplifier schematic diagrams)

The audio/signalling/filter/companding IC (ASFIC\_CMP) and the audio power amplifier, shown in Figure 1-2, form the main components of the audio/signalling architecture section of the controller board. Inputs include a 16.8 MHz clock from the synthesizer, recovered audio and squelch, MCU control signals, and external or internal microphones. Outputs include a microprocessor clock (uP), modulator output to the synthesizer, and amplified audio signals to an internal or external speaker.

## **Chapter 2**

## TROUBLESHOOTING CHARTS

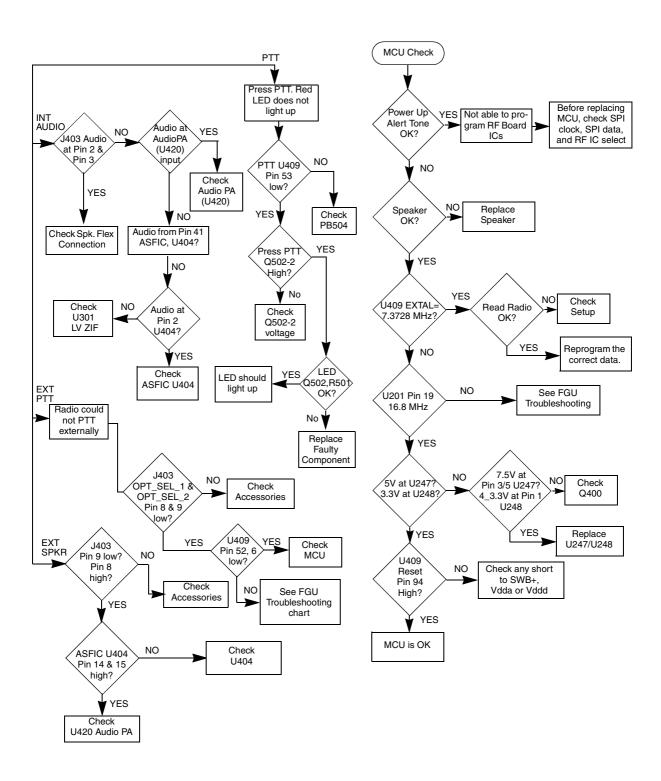

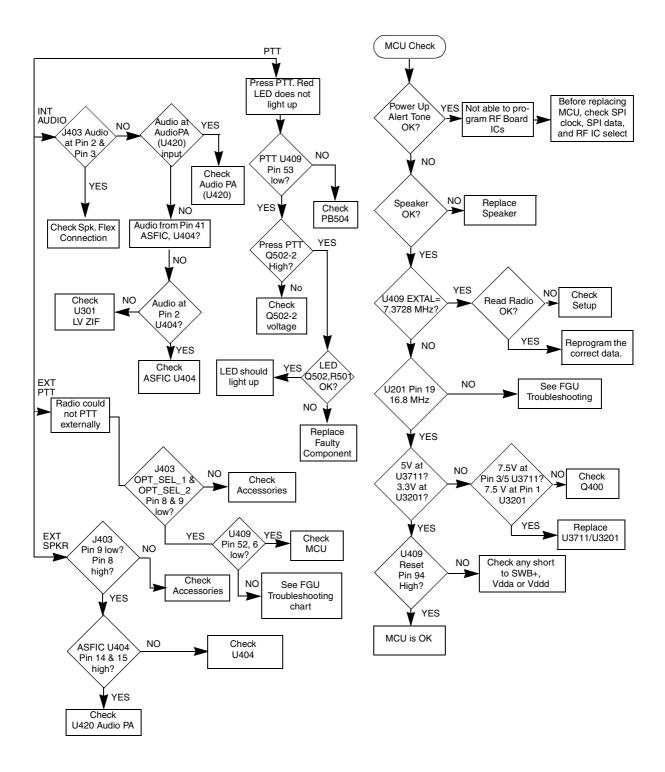

#### 1.0 UHF/ UHF2/ 300R1/800MHz Controller

#### 2.0 VHF Controller

Lowband Controller 2-3

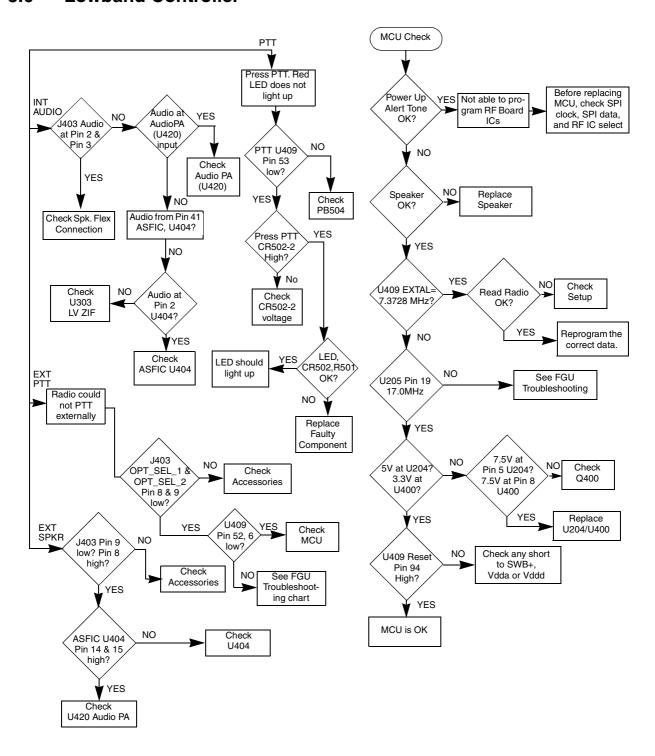

#### 3.0 Lowband Controller

## **Chapter 3**

## **CONTROLLER SCHEMATICS**

#### 1.0 Allocation of Schematics and Circuit Boards

The Controller circuits are contained on the printed circuit board (PCB) containing the RF circuits. This Chapter shows the schematics for the Controller circuits only, refer to the relevant RF section for details of the related RF circuits, the PCB component layouts and the Parts Lists. The Controller schematic diagrams and the related PCB and parts list are shown in the tables below:

Table 3-1 Schematics - Set 1

| PCBs:  8480450Z03  8485641Z02  8480587Z01  8485677Z01  8486062B12/ B14  8485726Z01  8480641Z03             | UHF UHF2 UHF GP1280 UHF2 GP1280 VHF 300 R1 800 MHz       |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| SCHEMATICS Overall Controller Schematic ASFIC/ ON_OFF Microprocessor Interface Memory Audio Power Amplifer | Page 3-3<br>Page 3-4<br>Page 3-5<br>Page 3-6<br>Page 3-7 |

Table 3-2 Schematics - Set 2

| PCBs:<br>8486101B09/B10                                                                                   | VHF GP1280                                                 |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| SCHEMATICS Overall Controller Schematic ASFIC ON_OFF Memory Microprocessor Interface Audio Power Amplifer | Page 3-9 Page 3-10 Page 3-10 Page 3-11 Page 3-12 Page 3-13 |

Table 3-3 Schematics - Set 3

| PCBs : 8485658Z01                                                                                         | Lowband                                                     |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| SCHEMATICS Overall Controller Schematic ASFIC ON_OFF Microprocessor Interface Memory Audio Power Amplifer | Page 3-15 Page 3-16 Page 3-17 Page 3-18 Page 3-18 Page 3-19 |

Table 3-4 Schematics - Set 4

| PCBs:<br>8486062B16                                                                                       | VHF                                                                        |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| SCHEMATICS Overall Controller Schematic ASFIC ON_OFF Microprocessor Memory Interface Audio Power Amplifer | Page 3-21<br>Page 3-22<br>Page 3-23<br>Page 3-24<br>Page 3-24<br>Page 3-25 |

Table 3-5Schematics - Set 5

| PCBs: 8480450Z13/14 8485641Z06 8485726Z04                                                                 | UHF<br>UHF2<br>300 R1                                                      |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| SCHEMATICS Overall Controller Schematic ASFIC ON_OFF Microprocessor Memory Interface Audio Power Amplifer | Page 3-27<br>Page 3-28<br>Page 3-29<br>Page 3-30<br>Page 3-30<br>Page 3-31 |